[总线概述]

\quad

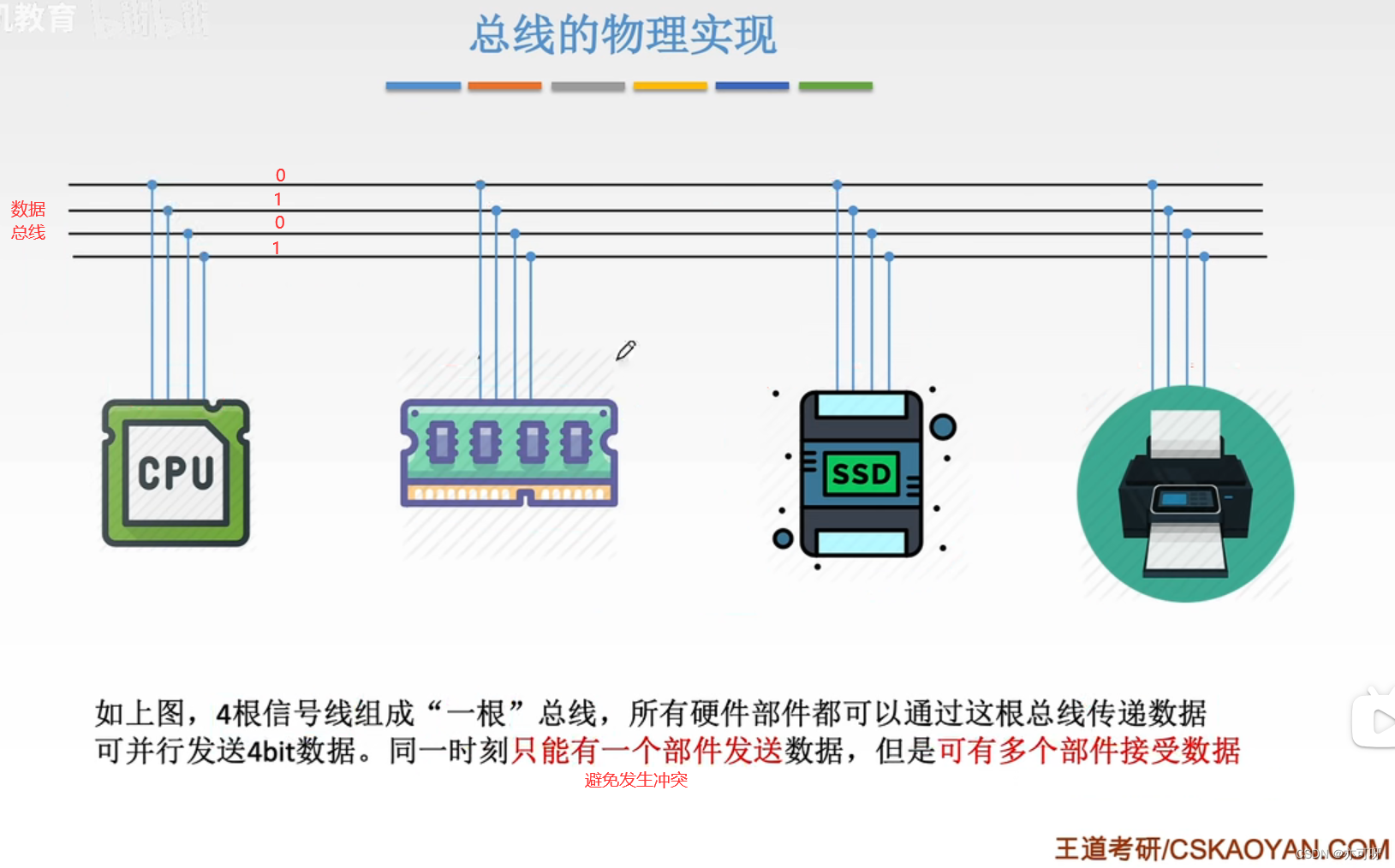

为什么数据总线或地址总线可以并行传输?

原因是每个总线可能由很多根信号线组成

\quad

要传输32bit就需要32根线

\quad

\quad

正片开始

\quad

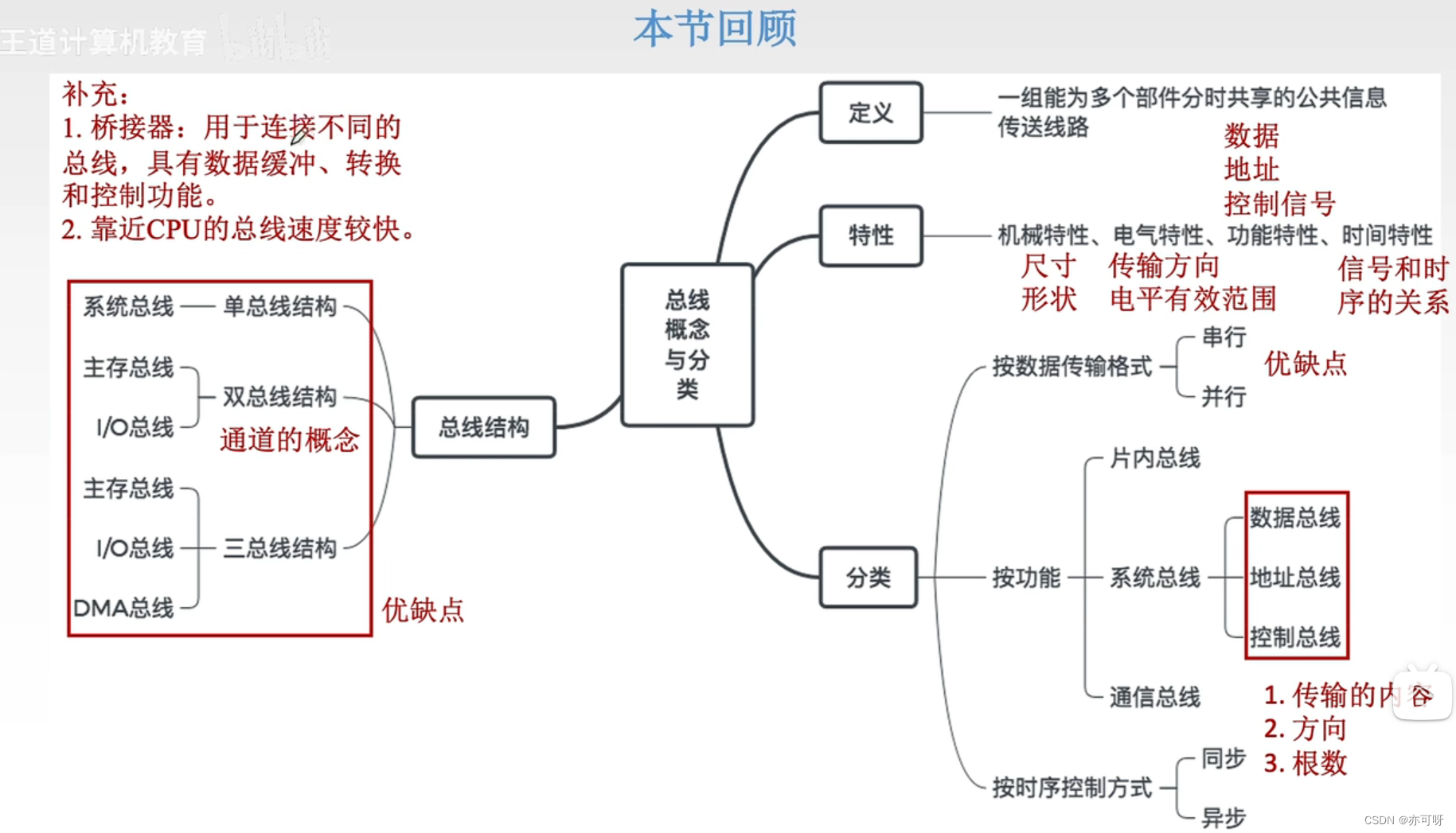

一. 基本概念

\quad

为了更好地解决I/o设备和主机之间连接的灵活性问题,计算机的结构从分散连接发展为总线连接。

共享是指总线上可以挂接多个部件,各个部件之间互相交换的信息都可以通过这组线路分时共享。

分时是指同一时刻只允许有一个部件向总线发送信息,如果系统中有多个部件,则它们只能分时地向总线发送信息。

\quad

\quad

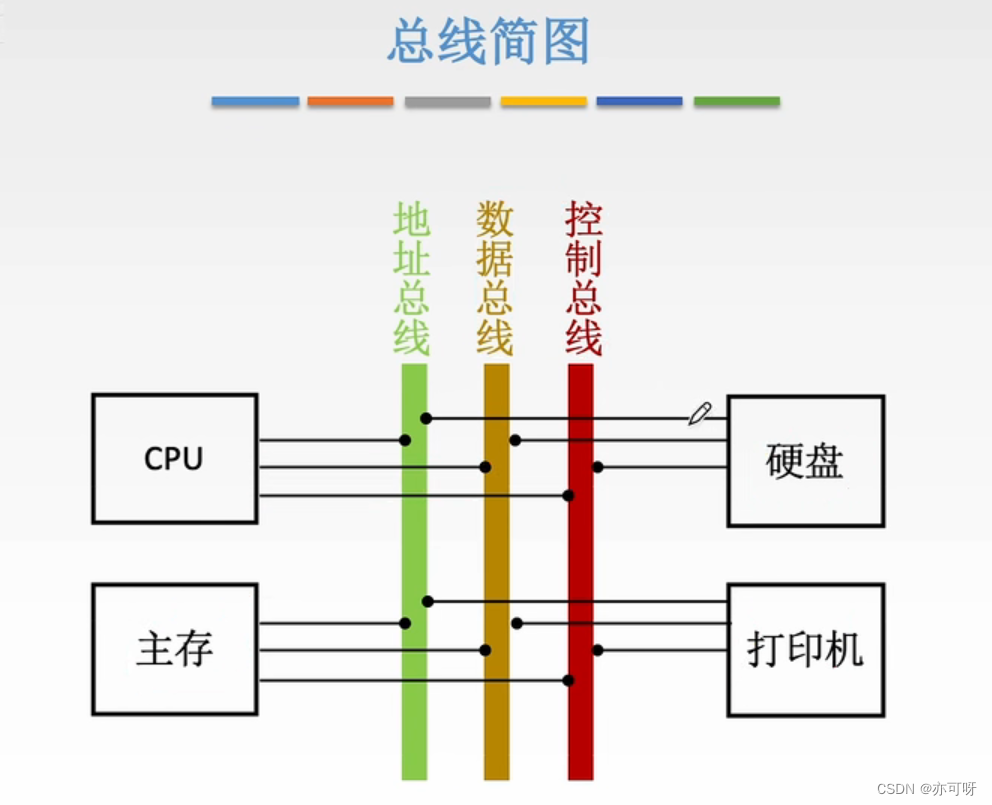

传输方向: CPU从地址总线给主存指明此次要读写的地址, 是单向的

\quad

\quad

\quad

\quad

CPU从数据总线往主存读写数据是双向的

有效的电平范围: 比如设低电平为0~0.5V

\quad

\quad

\quad

\quad

\quad

\quad

高电平为4.8~5.2V

\quad

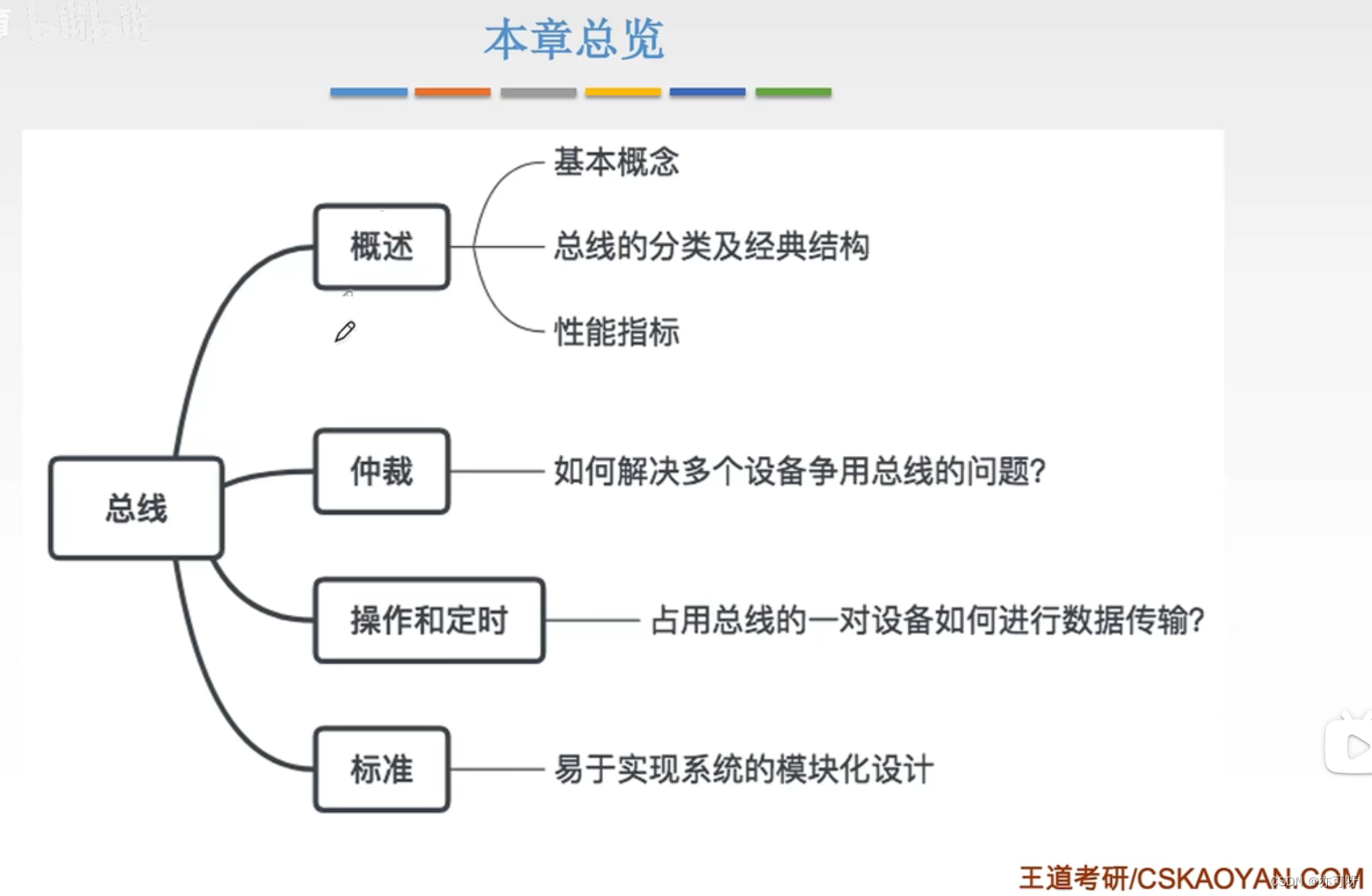

二. 总线的分类

\quad

\quad

\quad

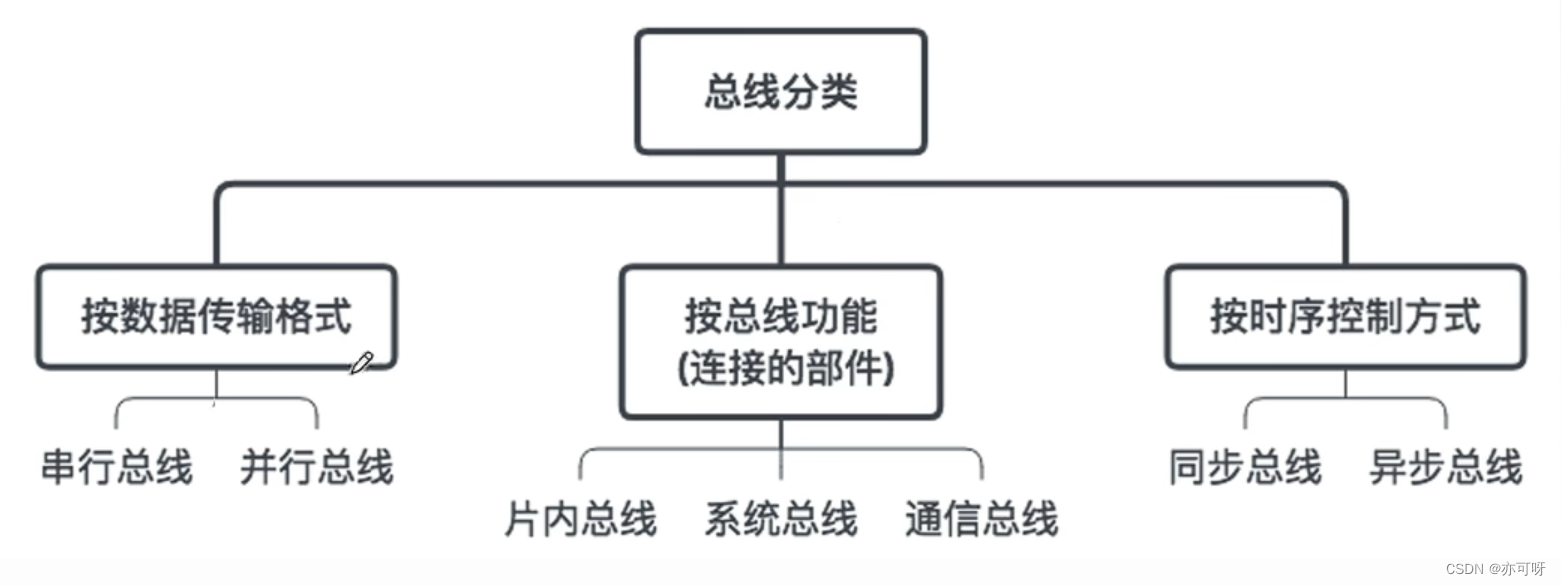

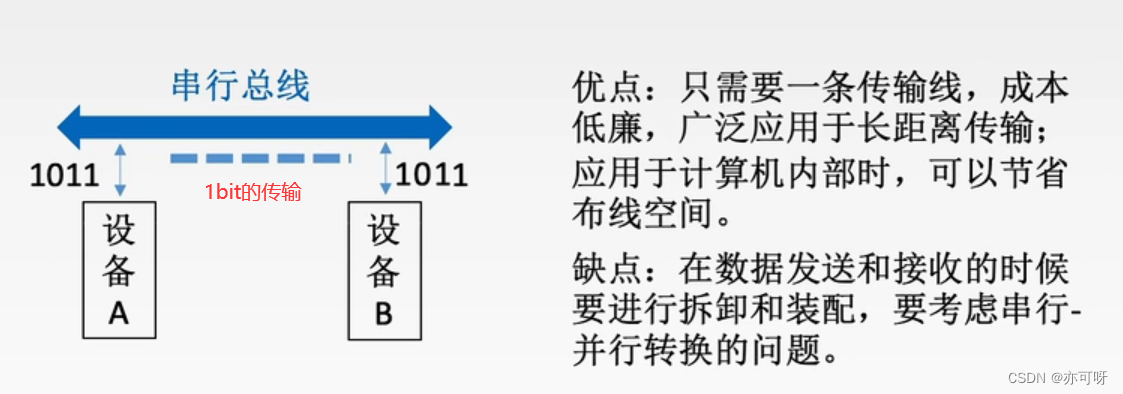

2.1 按数据传输格式

抗干扰能力强

USB是串行传输的, 就是1bit1bit传数据, 而CPU是并行传输的, 所以要考虑串行-并行转换问题

\quad

\quad

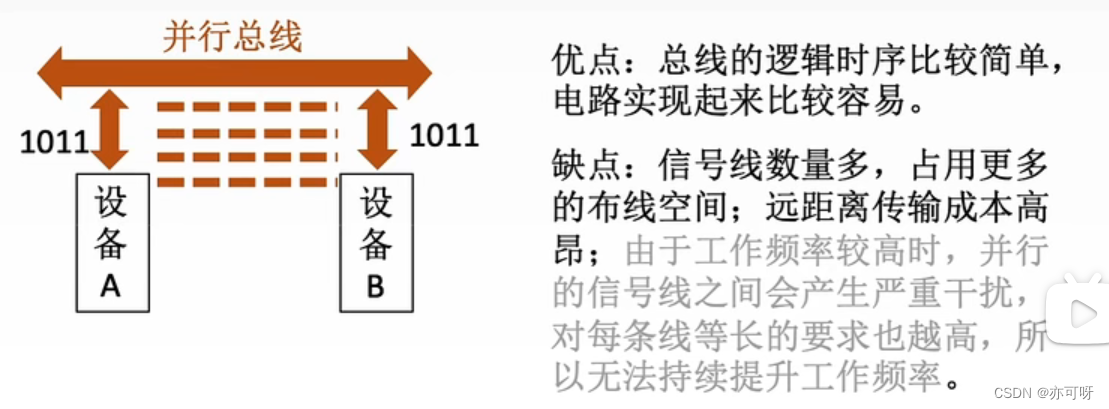

多bit同时传输, CPU与主存之间就是并行传输

由于并行传输信号线之间会产生严重干扰, 所以会影响传输频率上限, 所以说并行的传输速度不一定比串行的传输速度块

\quad

\quad

2.2 按总线功能(连接的部件)

2.21 片内总线

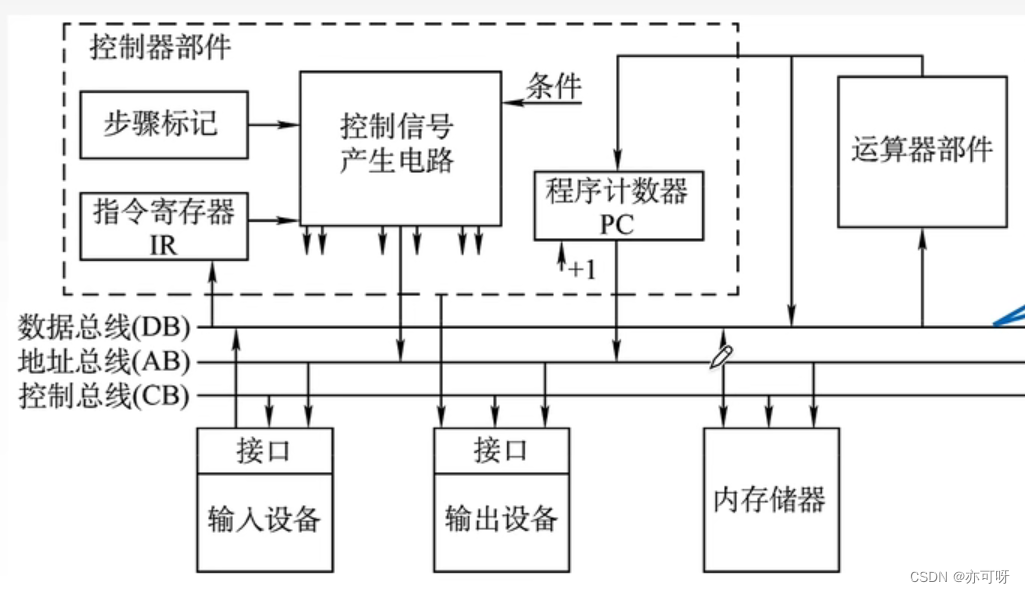

片内总线是芯片内部的总线。

它是CPU芯片内部寄存器与寄存器之间、寄存器与ALU之间的公共连接线。

\quad

2.22 系统总线

系统总线是计算机系统内各功能部件(CPU、主存、I/O接口)之间相互连接的总线。按系统总线传输信息内容的不同,又可分为3类:数据总线、地址总线和控制总线。

2.1 数据总线: 传输各功能部件之间的数据信息,包括指令和操作数;位数(根数)与机器字长、存储字长有关; 双向传输。(根数如果是机器字长的一半, 那么就要分两次传,才能传完)

\quad

2.2 地址总线: 传输地址信息,包括主存单元或I/O端口的地址;

位数(根数)与主存地址空间大小及设备数量有关;单向传输。

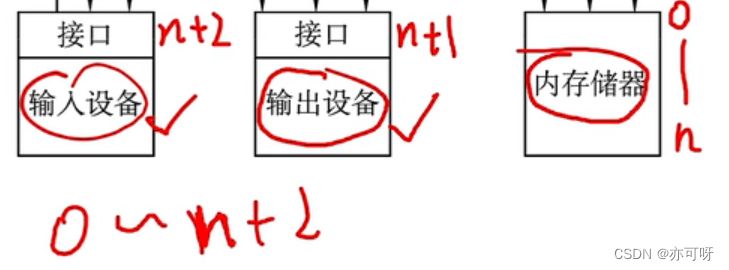

比如内存地址是0~n, 还有两个设备, 地址是到n+2

那么就需要0~n+2这么多根地址线

\quad

2.23 控制总线: 一根控制线传输一个信号

有出:CPU送出的控制命令; 单向

有入:主存(或外设)返回CPU的反馈信号。单向

(双向但不同时)

\quad

注意区别:

数据通路表示的是数据流经的路径, (逻辑概念)

数据总线是承载的媒介, (物理概念)

\quad

系统总线的结构: 单总线结构、双总线结构、三总线结构

单总线结构

- 结构:CPU、主存、I/O设备(通过I/O接口)都连接在一组总线上,允许I/O设备之间、IO设备和CPU之间或IO设备与主存之间直接交换信息。

- 优点:结构简单,成本低,易于接入新的设备。

- 缺点:带宽低、负载重,多个部件只能争用唯一的总线,且不支持并发传送操作。

但是CPU和主存速度快, 设备传输速度慢, 一起接在系统总线上显然是会拖累的

\quad

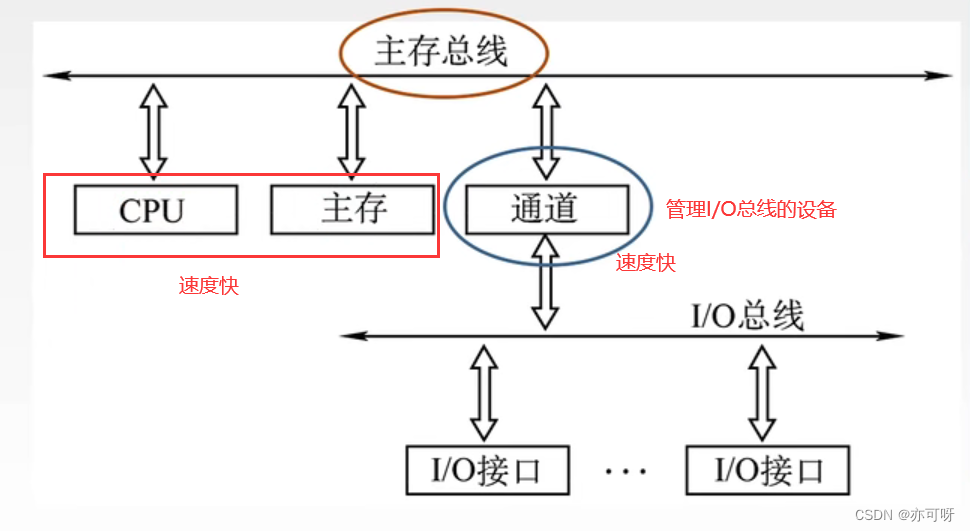

双总线结构

- 结构:双总线结构有两条总线,一条是主存总线,用于CPU、主存和通道之间进行数据传送;另一条是I/o总线,用于多个外部设备与通道之间进行数据传送。

- 优点:将较低速的I/O设备从单总线上分离出来,实现存储器总线和I/O总线分离。

- 缺点:需要增加通道等硬件设备。

主存总线支持突发(猝发)传送:送出一个地址,收到多个地址连续的数据(有一些指令序列是需要访问连续地址的数据, 这样就提高了效率)

\quad

三总线结构

CPU可以通过主存总线和DMA总线向磁盘机取数据, 而不必经过慢速的I/O总线

- 结构:三总线结构是在计算机系统各部件之间采用3条各自独立的总线来构成信息通路这3条总线分别为主存总线、/o总线和直接内存访问DMA总线。

- 优点:提高了I/o设备的性能,使其更快地响应命令,提高系统吞吐量。

- 缺点:系统工作效率较低。(三条总线同一时刻只能有一条在工作)

\quad

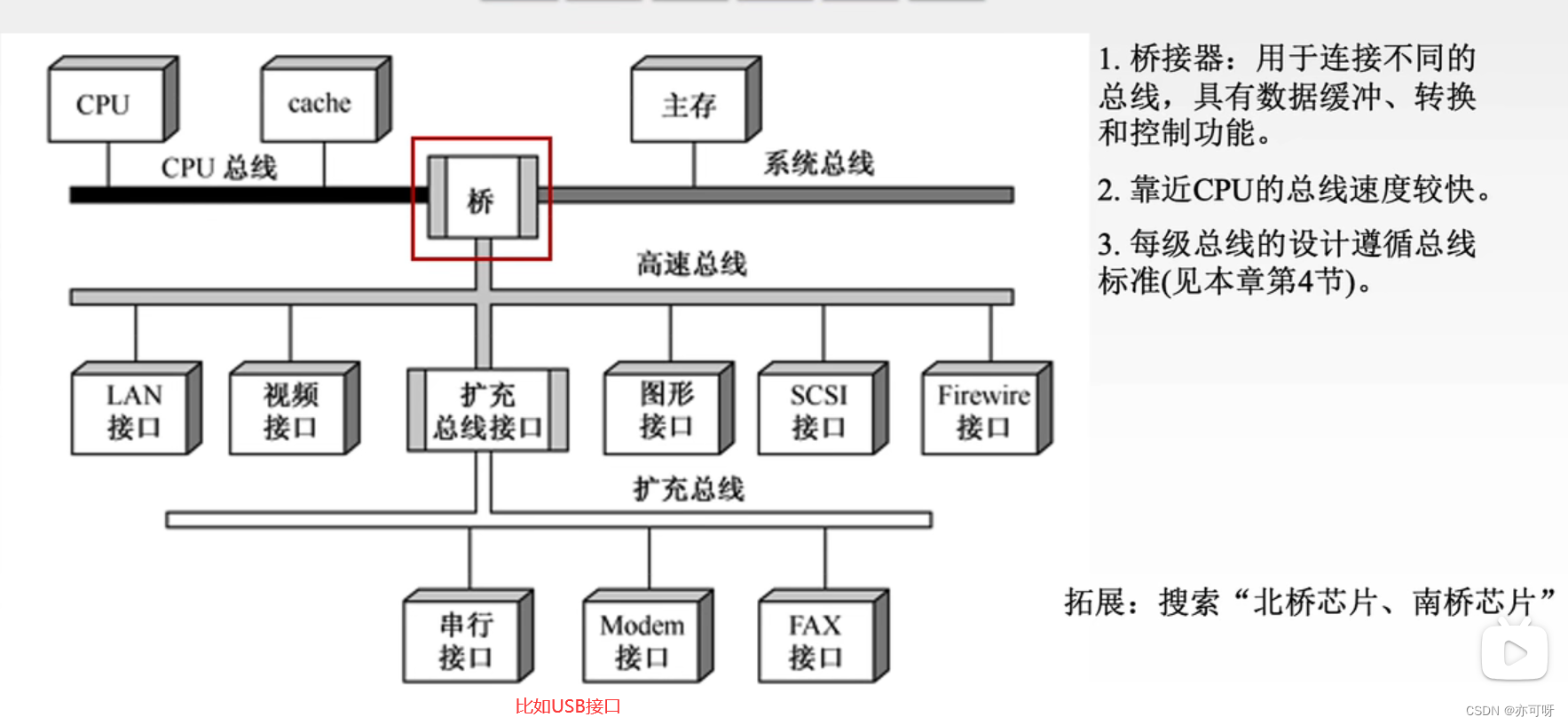

四总线结构(拓展)

现代一般用四总线

\quad

2.3 通信总线

通信总线是用于计算机系统之间或计算机系统与其他系统(如远程通信设备、测试设备)之间信息传送的总线,通信总线也称为外部总线。

\quad

\quad

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!