【验证概括 & SV的数据类型_2023.12.18】

验证概括

验证的过程是保证芯片实现符合规格说明书(Specification,spec)的过程

验证的两项任务:

RTL sim:前仿真,验证功能

GLS-Gate (Level Simulation):后仿真,验证功能和时序

验证功能点

产生激励

分析DUT/DUV(design under test/verification)(就是设计代码RTL)的输出

前仿真与后仿真

RTL前仿真流程:

理解DUT → 制定验证策略方法提取验证点+搭建平台 → 执行平台 → 检查覆盖率

后仿真流程:

环境准备DUT(netlist+SDF)+选择Case(考虑关键路径、频率、速率) → 后仿真及Violation分析

SDF(standard Delay Format):后端经PR布局布线之后生成的包含网表中各器件单元延时、走线延时、信号宽度、时序要求等信息的文件

动态与静态时序分析

动态时序分析

根据电路中提取的延时参数,通过仿真软件动态的仿真电路以验证时序是否满足要求(后仿真)

静态时序分析

通过分析设计中所有可能的信号路径以确定时序约束是否满足时序规范(数字后端工程师)

SV数据类型

SV:用于验证的语言

UVM:用于验证的方法学

initial:只执行一次,本身不可综合,可在module,interface,program中使用

always:只可在module或interface中使用

SV中,module/interface硬件,program/class软件

内建类型(基本数据类型)

verilog中数据类型分为variable(reg,integer,time)和net(wire,wor,wand)型,都为四值逻辑

SV中数据类型有两个属性:type(区分variable和net)和data type(区分4值与2值)

variable可4可2值,net只能4值

SV新数据类型 logic,不用区分reg还是wire,但不能被多驱动(不能使用inout)

logic:4值;bit:2值(引入的原因:减少内存消耗,提高性能)

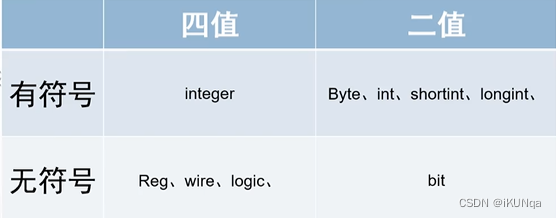

四值:integer reg logic net-type(wire tri)

二值:byte shortint int longint bit

有符号:byte shortint int longint integer

无符号:bit logic reg net-type(默认单比特,标量)

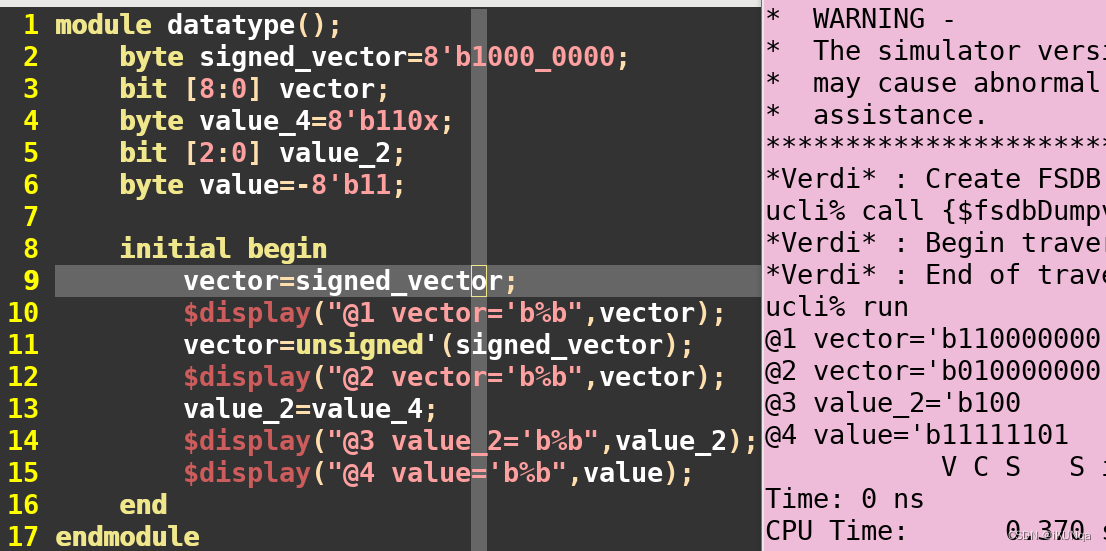

result_vector=unsigned'(signed_vector);//有符号数转换为无符号数

2值逻辑中没有x,会转变为0

有符号数高位补符号位,无符号数高位补0

数组 定长的,元素一致,有序

定宽数组:

int m[0:15];//16个整数[0],[1]...

int n[16];//16个整数[0],[1]...

多维数组:

int array[0:1][0:2];//6个存储单元,每个存储单元都是int型

int array[2][3]='{'{0,1,2},'{3,4,5}};//非合并数组,'{0,1,2}给array[0],'{3,4,5}给array[1]

==初始化前访问数组成员,logic返回X(四值),int或bit返回0(二值)==

动态数组:

合并数组:连续存放

bit [3:0][7:0] bytes;//用32bit

$display("%h",bytes[3][7]);//结果1,注意和多维数组的区别

非合并数组:不需把数据当作一个整体来访问

bit [7:0] b_unpack[3];//每个b_unpack[]给32bit,只用8bit,浪费空间

int [7:0] b_unpack[3];//语法错误,不可以是多bit数据类型,只能设为reg/logic/bit单比特类型

数组操作:循环 复制 比较

foreach遍历多维数组foreach(md[i,j])

a=b;//直接数组b复制给数组a

==和!=进行比较,结果仅限于内容相不相同

队列(可变长的):先进先出

int q[$]={0,2,5};

q={};//删除整个队列

q[$]={0,2,5};

q[1:$]={2,5};//$在右边表示最大

q[$:1]={0,2};//$在左边表示最小,在右边表示最大

结构体

数据的集合(可包含不同数据类型元素),使用不多(类可实现)

struct和typedef struct(重定义新数据类型)的使用

声明变量一定要放在initia块前面

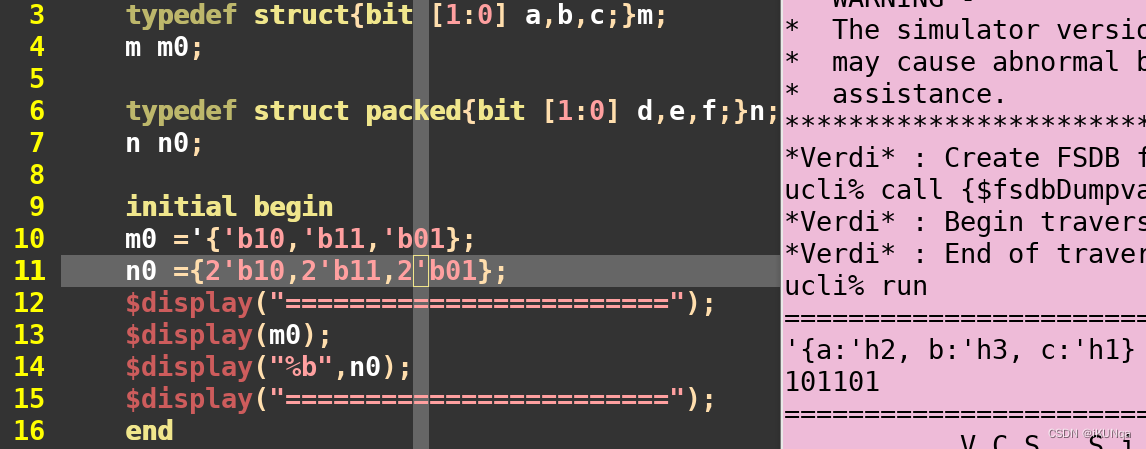

合并与非合并结构体

非合并赋值方式student1='{18,222,“aa”};不可以student1={18,222,“aa”};

压缩和非压缩结构体:

typedef struct packed{bit [1:0] a,b,c}s;//c,b,a连续存

typedef struct {bit [1:0] a,b,c}student;//c,b,a分别存

非压缩结构体赋值要加“ ’ ”,如11行不加会报错

压缩结构体赋值可加可不加“ ’ ”,但要注明位宽,不然赋值易出错

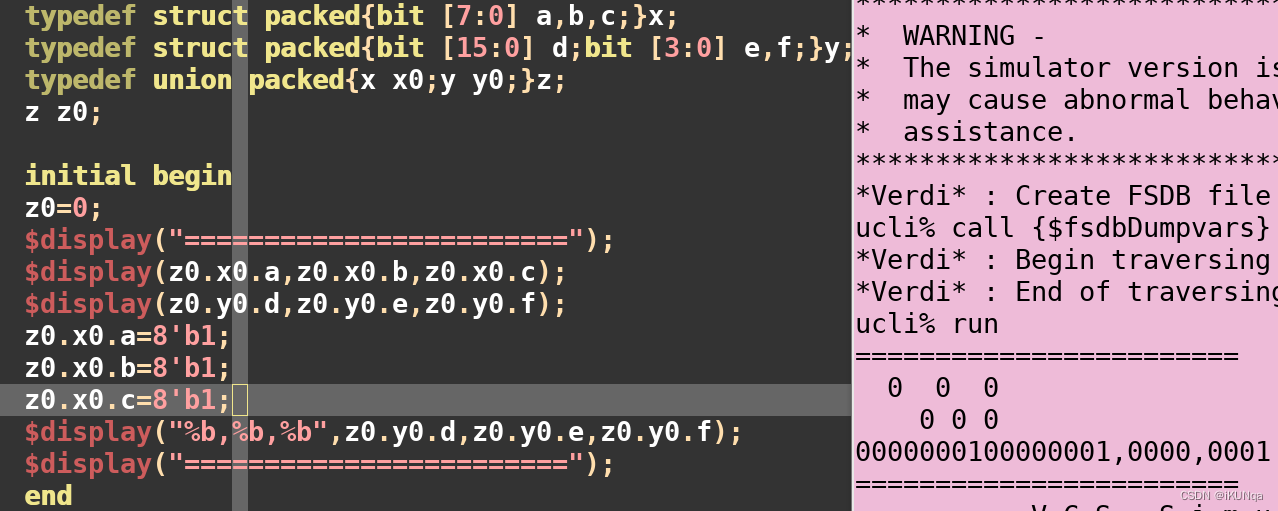

联合结构体union

x改变,y改变,成员公用一块内存空间,一个改变其他的也改变

x改变,y改变,成员公用一块内存空间,一个改变其他的也改变

typedef union packed{bit[7:0] a; byte b;}s;//必须是压缩的共享空间,成员一个位宽

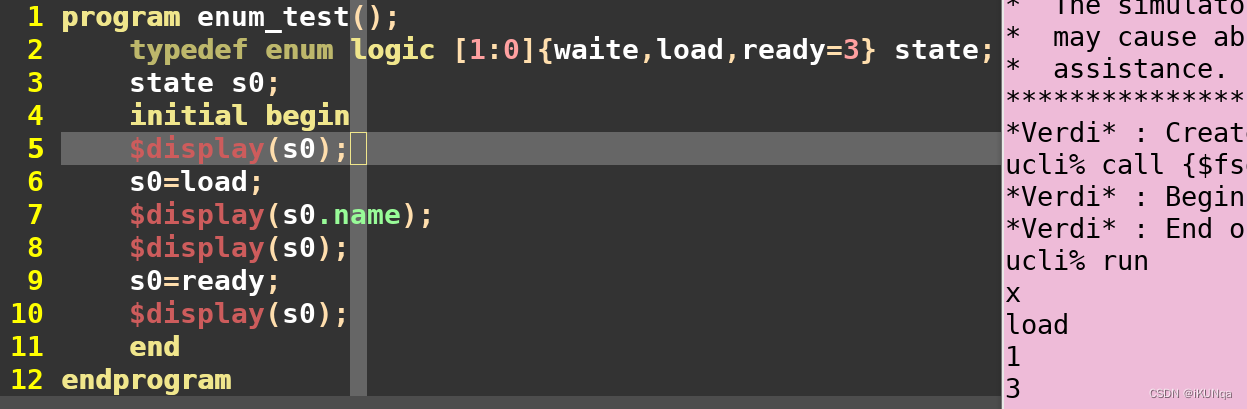

枚举类型

默认int类型,默认0,1,2……,没有定义,后一个值是前一个加一

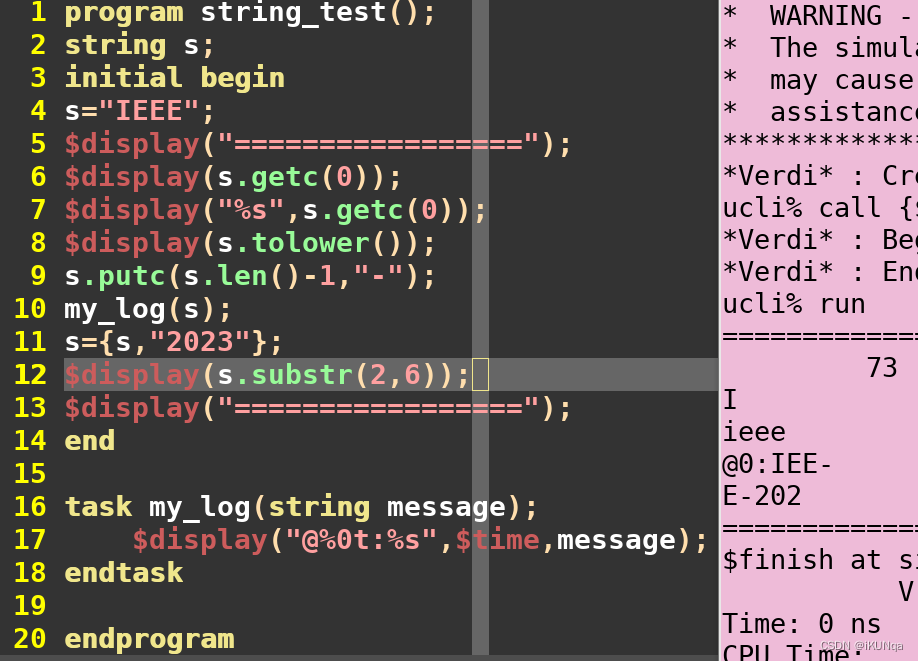

字符串 可变长

str.toupper()//转成大写

str.tolower()//转成小写

str.putc(i,c)//字符输入,将字符串str中第i个字符替换为字符c

str.substr(i,j)//子串,由str的第i和第j个中间的所有字符组成

strA.compare(strB)与strA.icompare(strB)//结果相同,相同为0,不同为1或-1

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!