实验九 基于FPGA的计数译码显示电路设计

2023-12-30 18:24:40

基本任务一:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-3输入BCD码,用SW4-7控制数码管位选

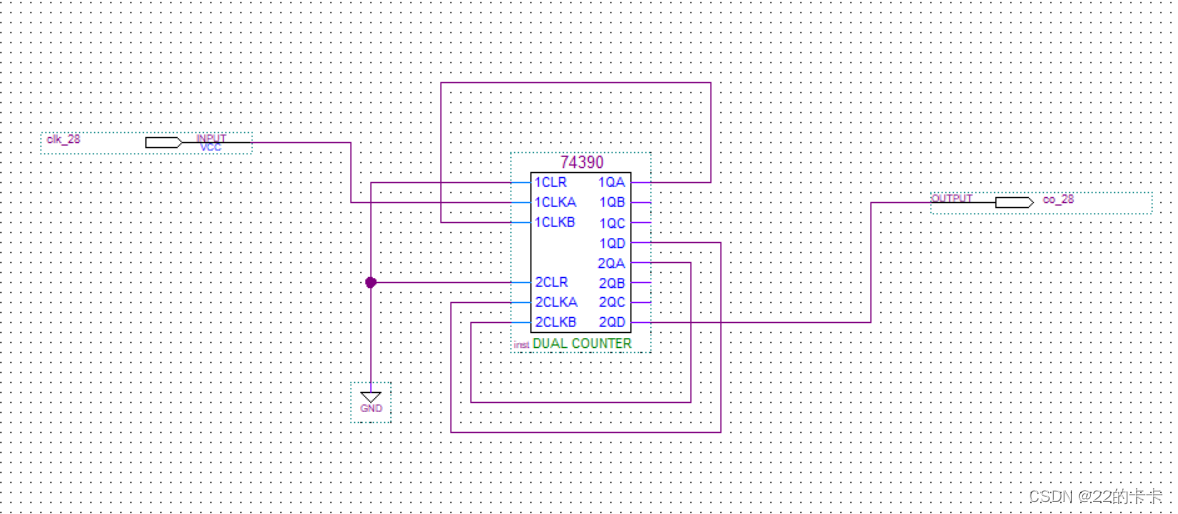

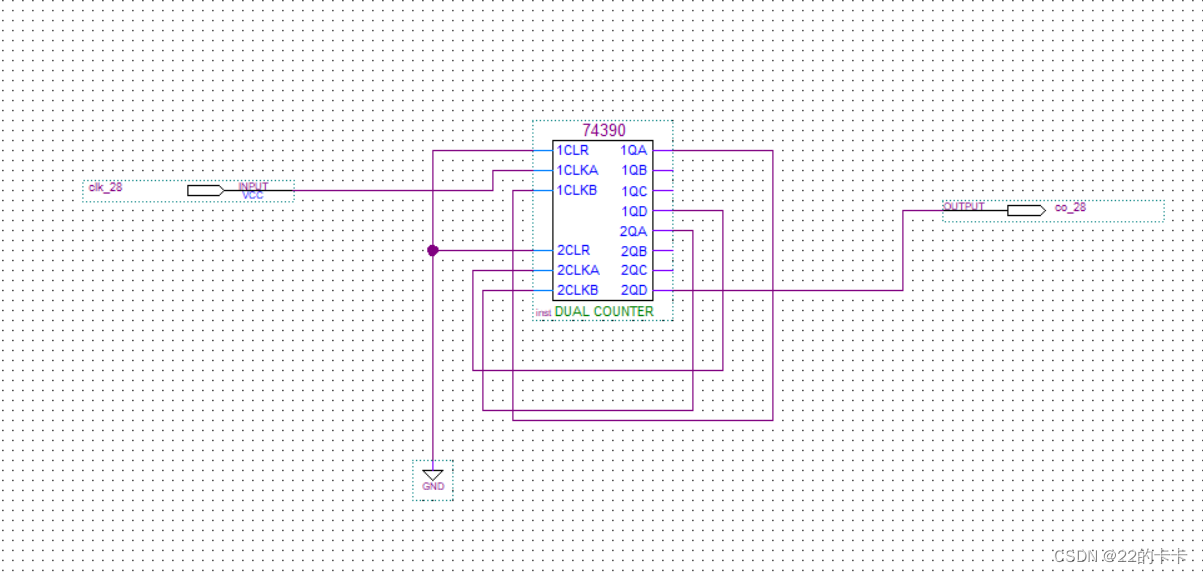

m100:

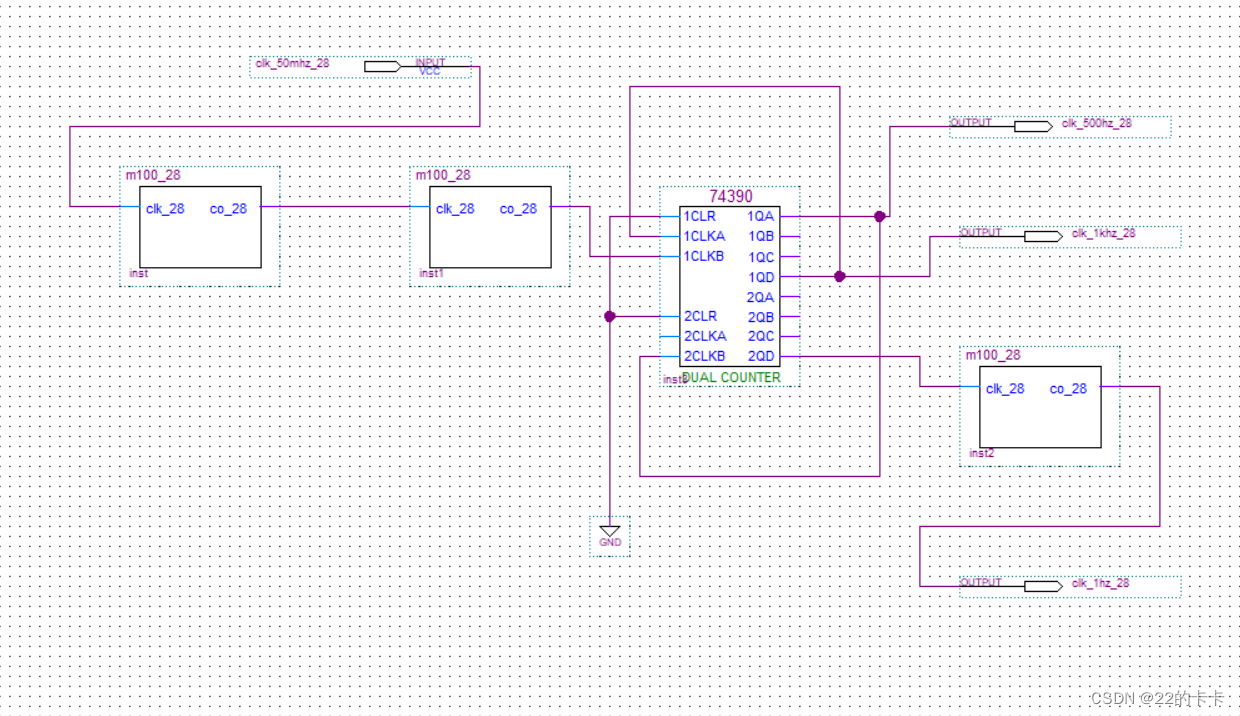

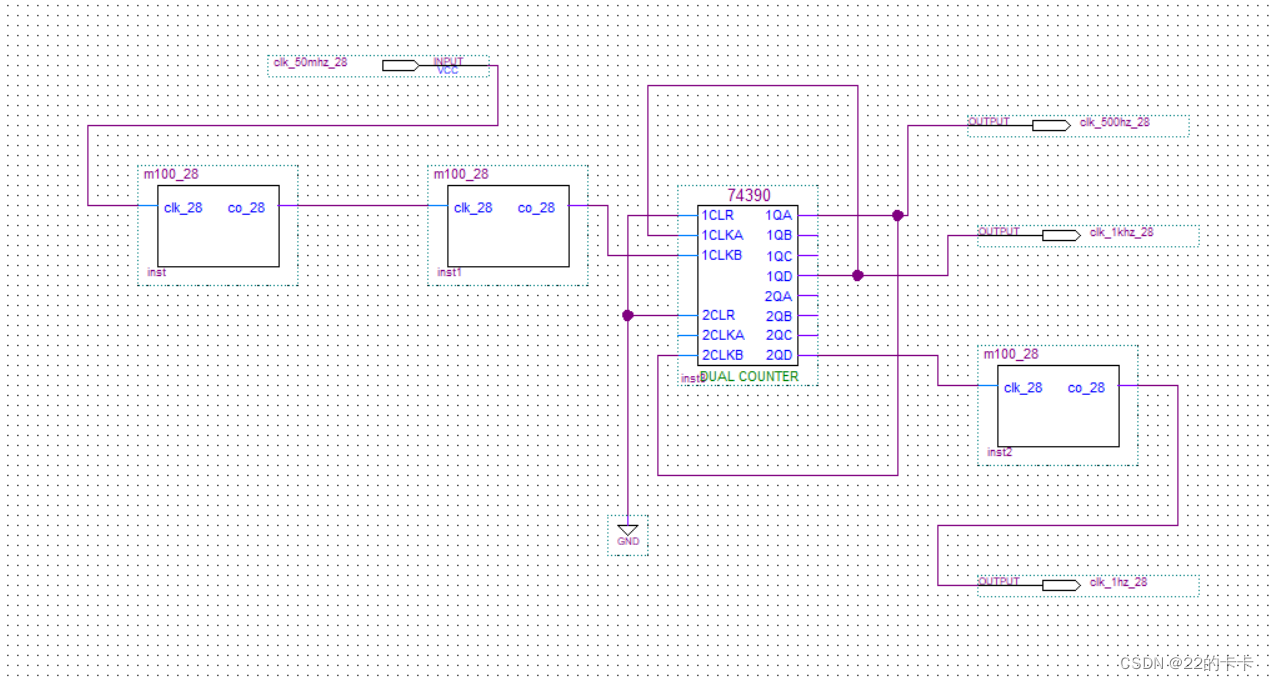

frediv:

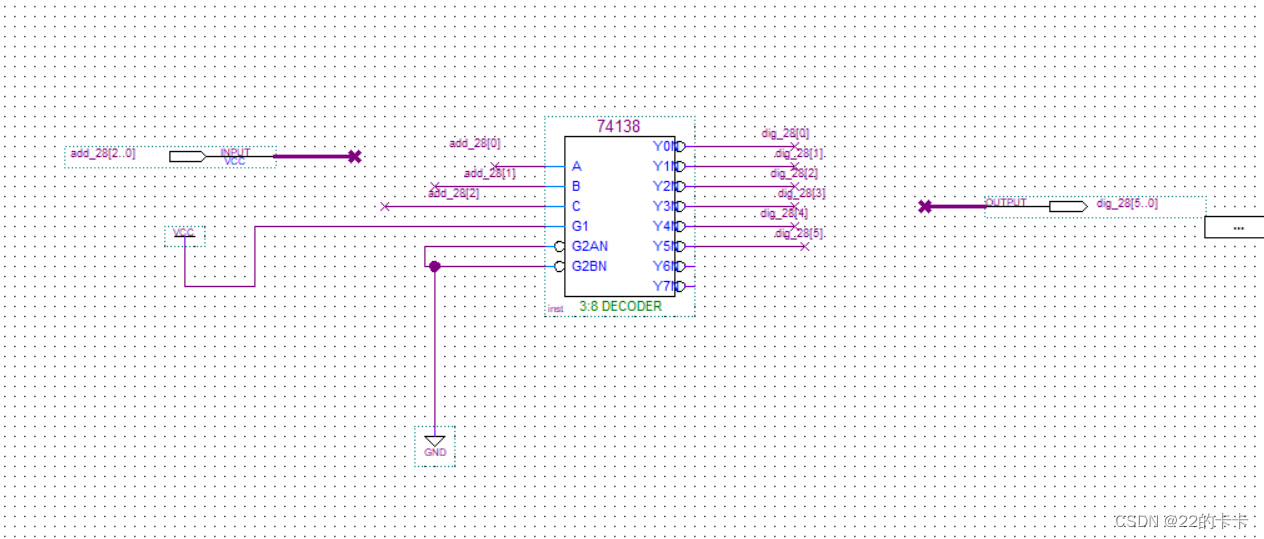

decoder:

基本任务二:利用FPGA硬件平台上的4位数码管显示m10技术结果

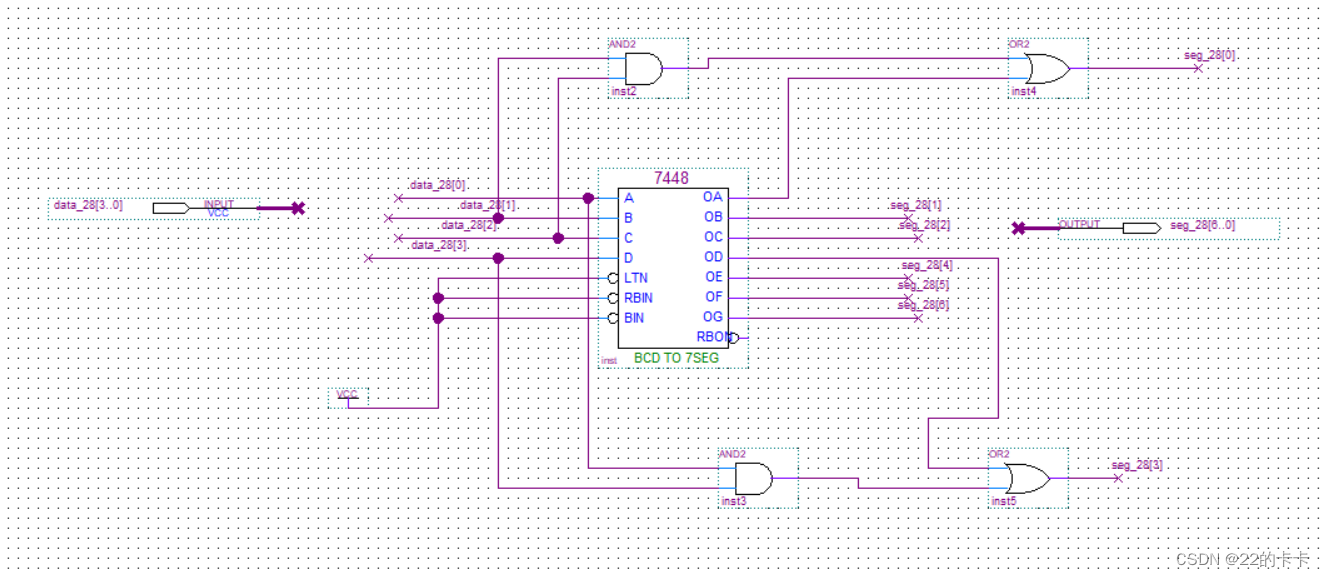

扩展任务一:对7448译码的6和9进行补段

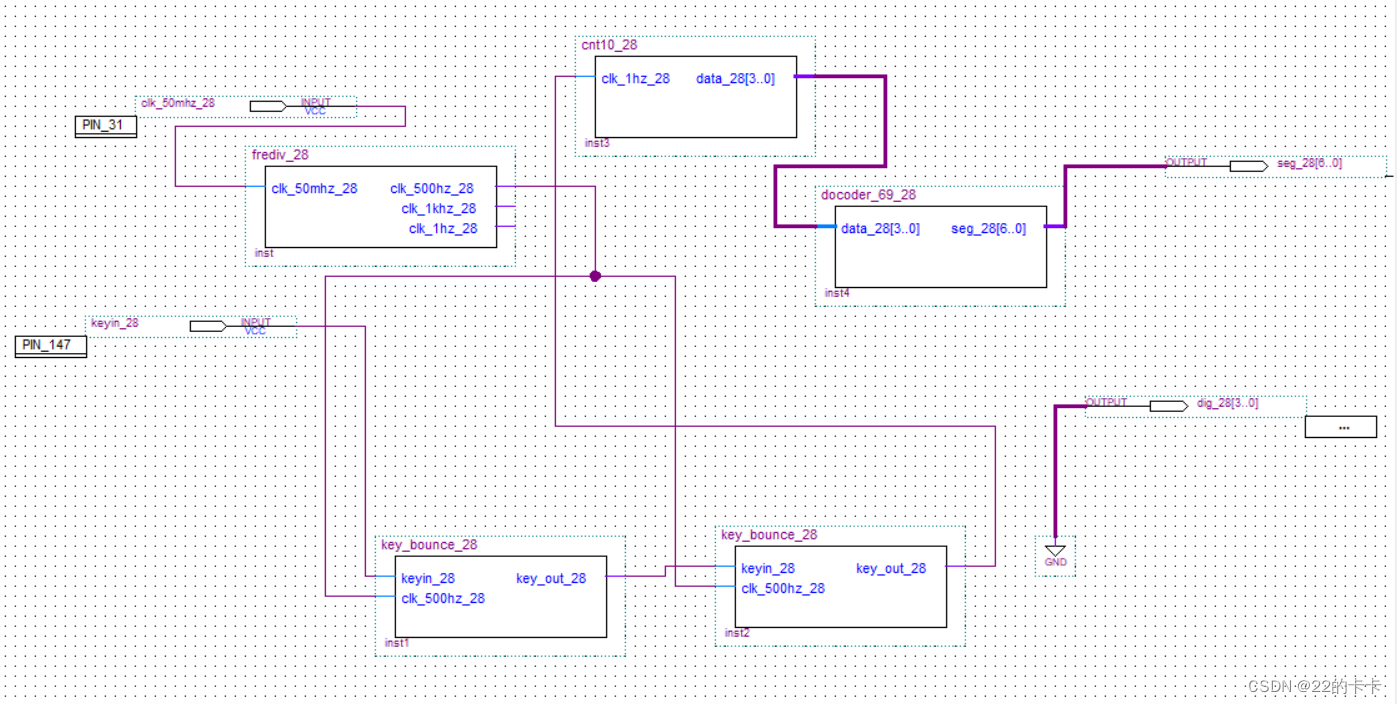

扩展任务二:用按键控制计数器从0-9计数,4位数码管显示技术结果。

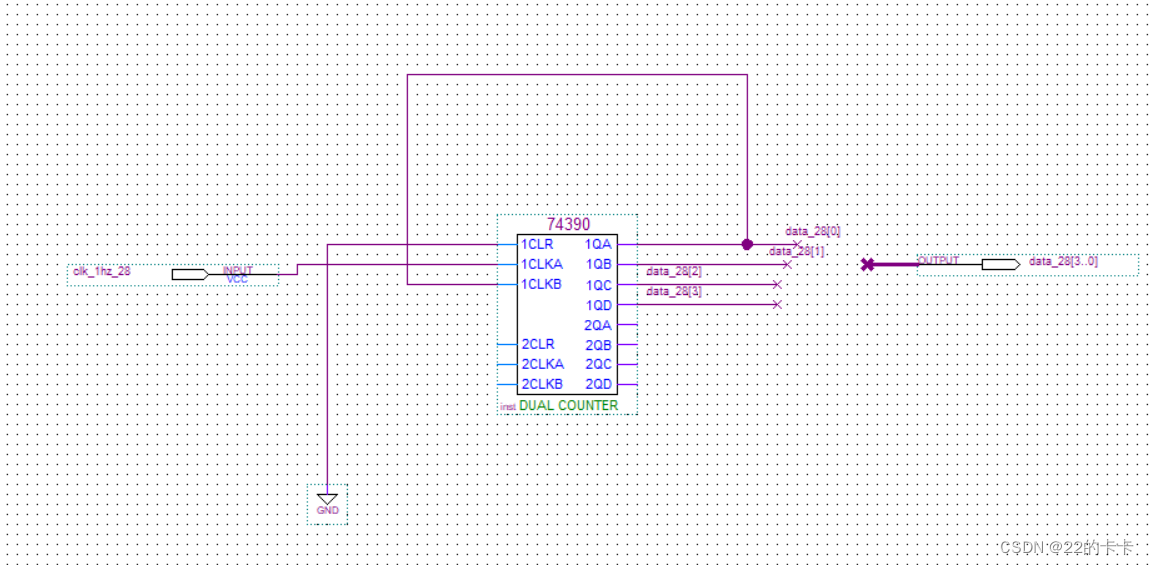

cnt10:

decoder69:

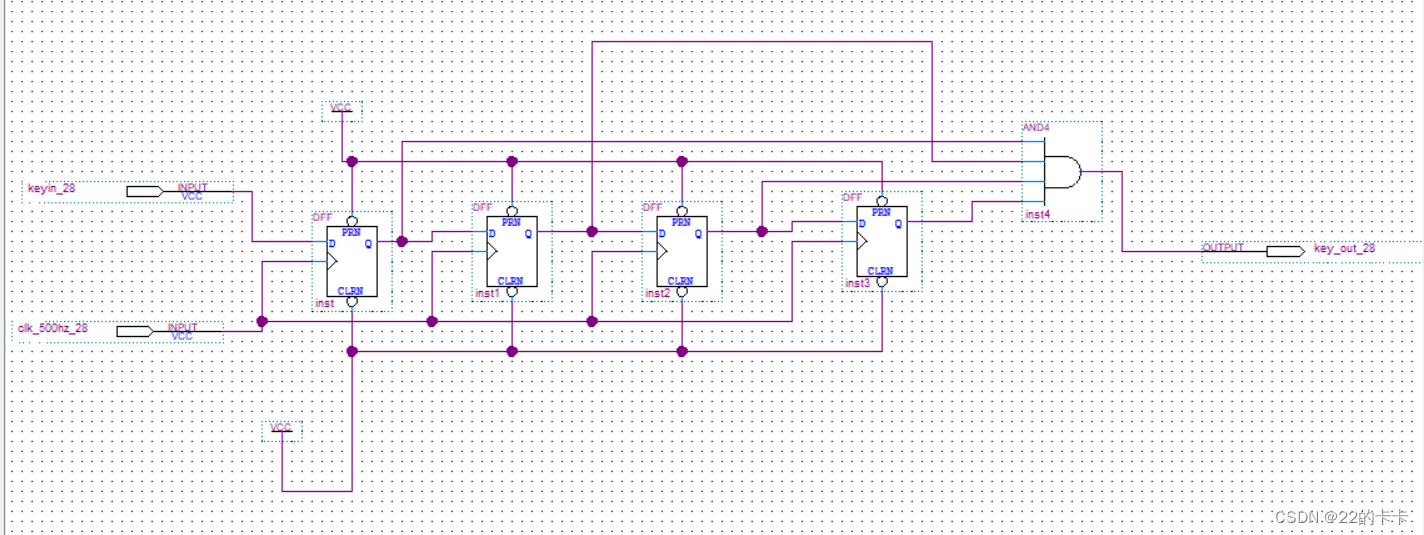

key_bounce:

frediv:

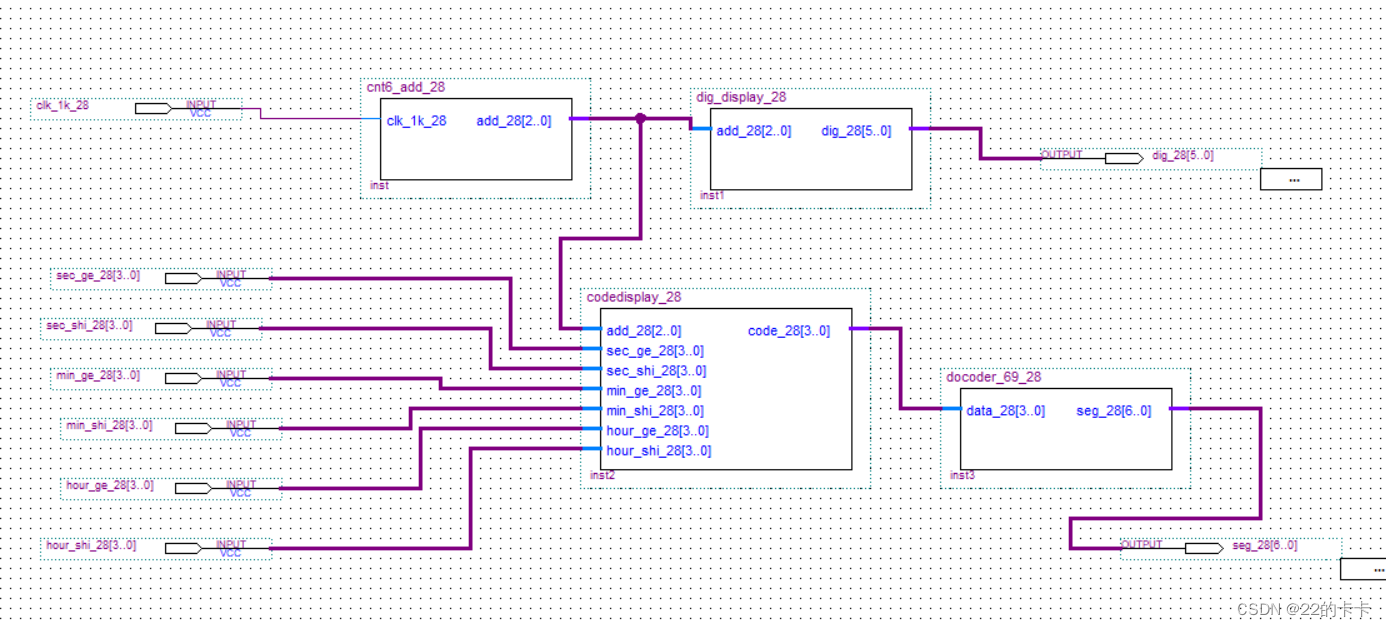

基本任务三:利用FPGA硬件平台上的6位数码管显示模100计数结果。

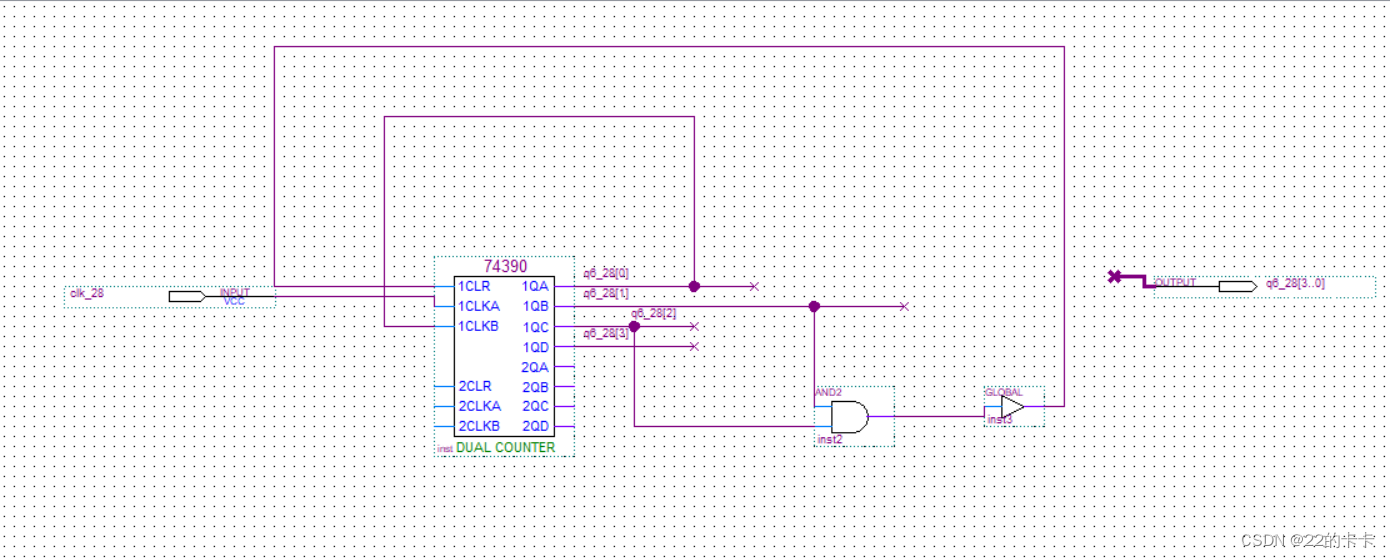

cnt6:

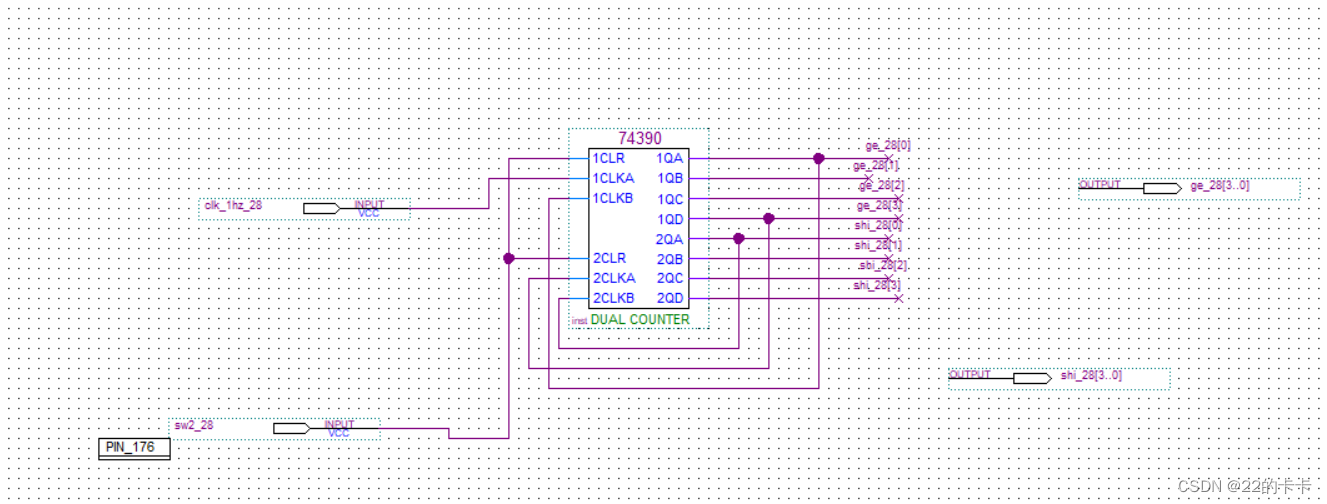

m100:

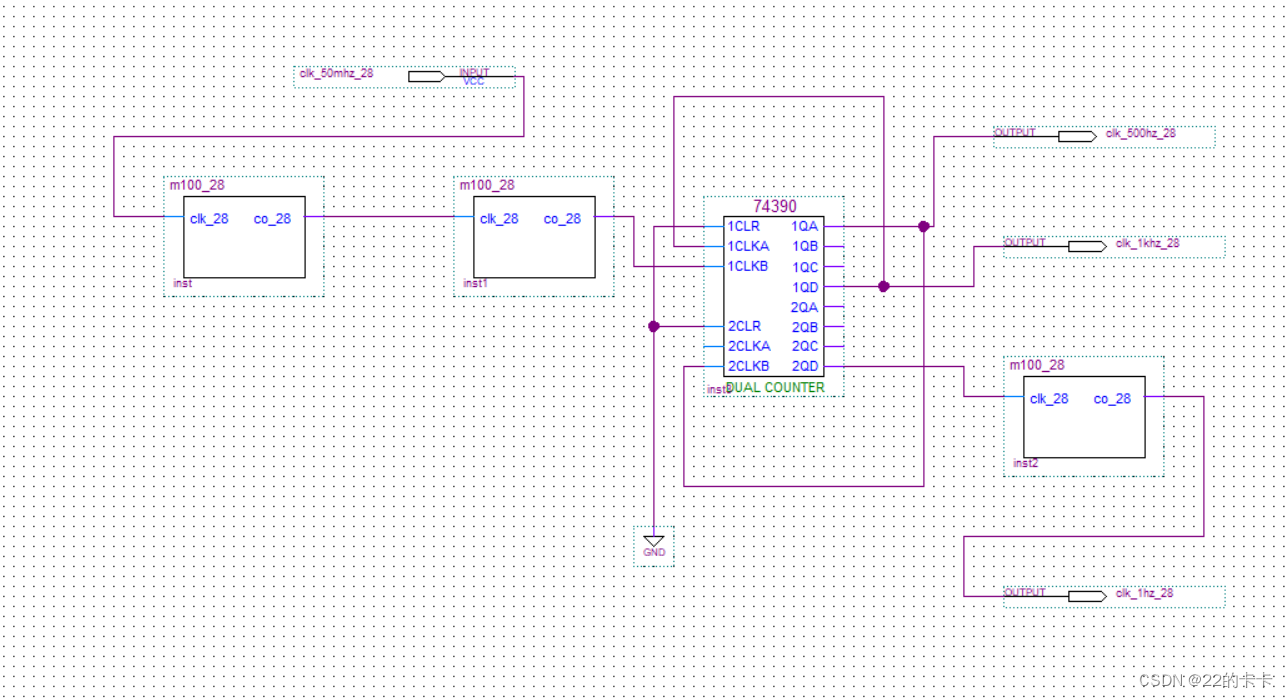

frediv:

decoder——69:

m100_2output:

dig_select:

code_select:

display_m100:

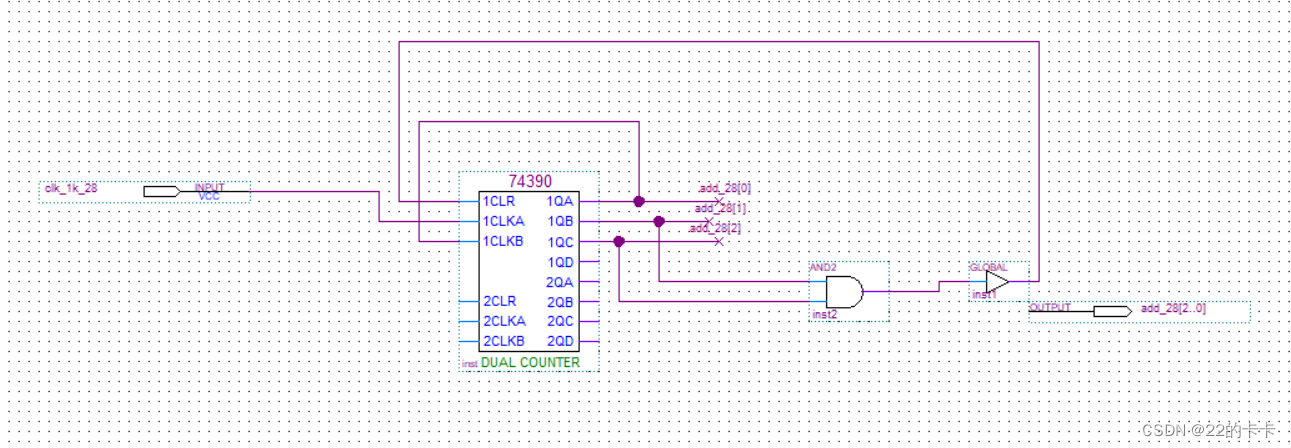

cnt6_add

文章来源:https://blog.csdn.net/m0_73605862/article/details/135306785

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!