基于ZU19EG的100G-UDP解决方案

- 概述

本文档介绍ZU19EG与Mellanox CX6 100G网卡通信解决方案。

- 环境配置

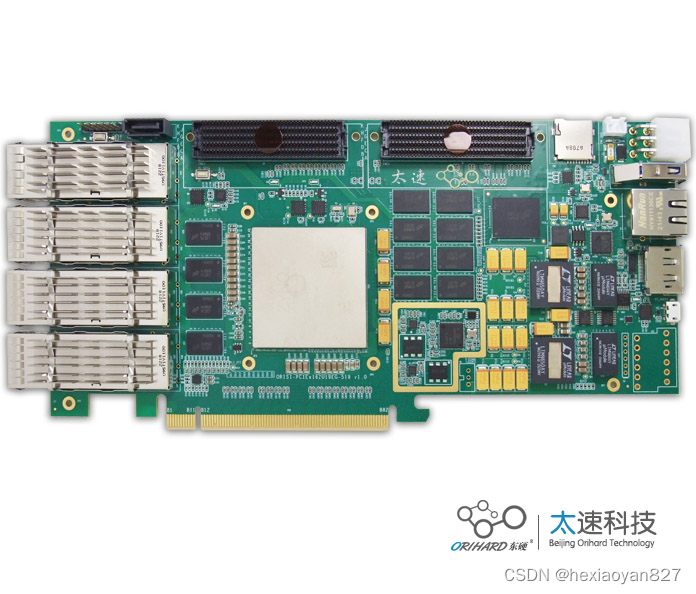

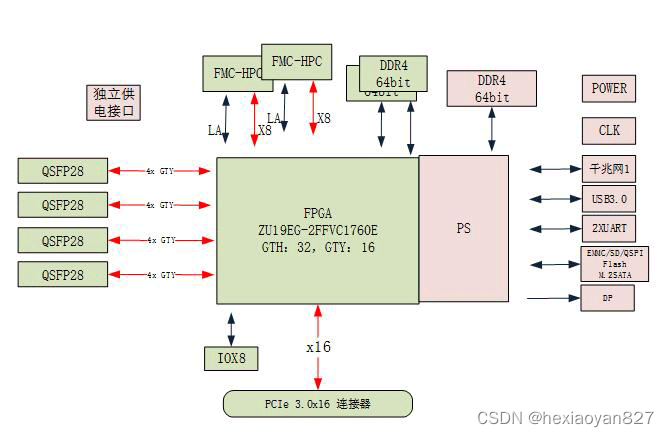

FPGA硬件:519-ZU19EG的4路100G光纤PCIe加上计算卡

电脑:国产国鑫主板(双PCU):Gooxi G2DA-B ?CPU:Intel Xeon Silver @2.2GHz 内存:64GB?操作系统:ubuntu20.04

网卡:ConnectX6 MCX653106A-ECA_Ax

- FPGA解决方案

板卡fpga型号:XCZU19EG-FFVC1760-2E

开发环境:Vivado2021.2

输出:QSFP28光口输出

工程代码架构如下:

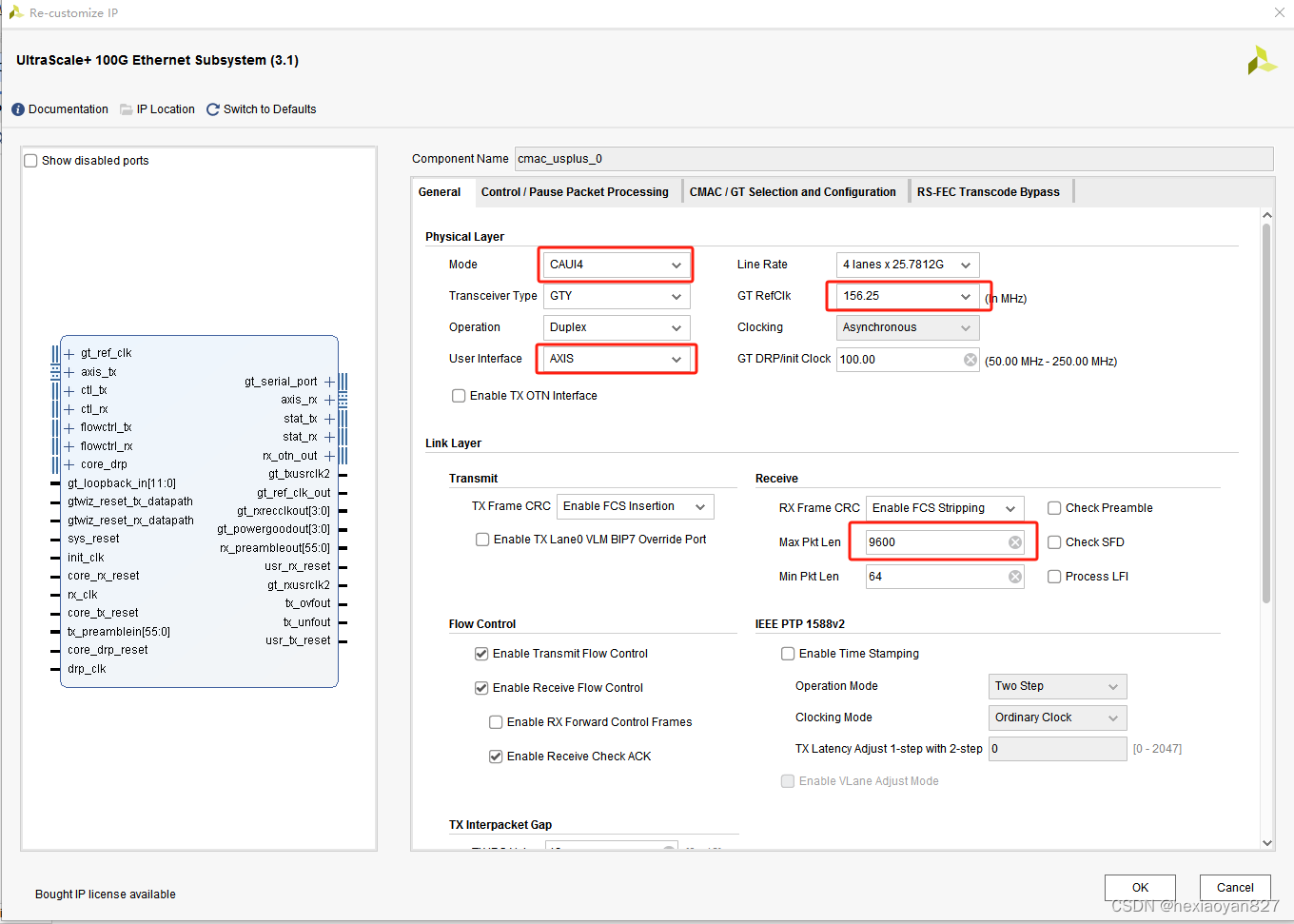

UltraScale+ 100G Ethernet Subsystem配置如下:

工程代码各模块功能:

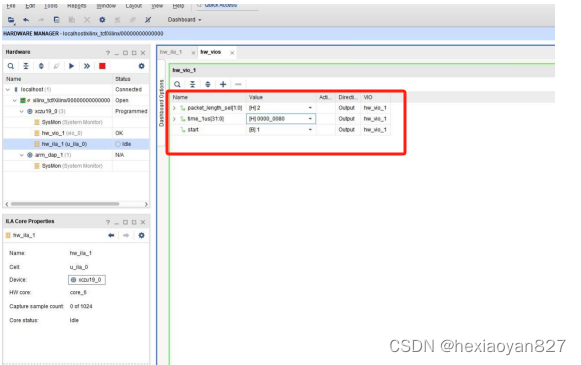

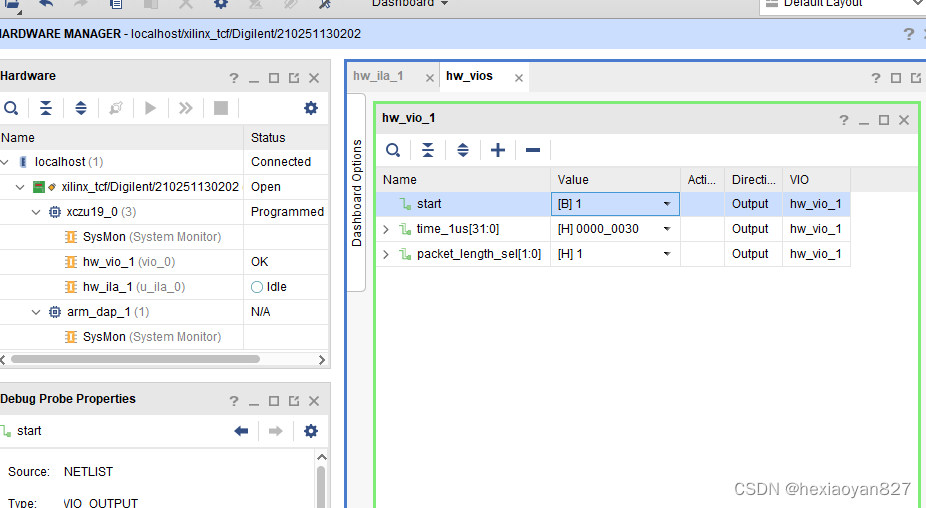

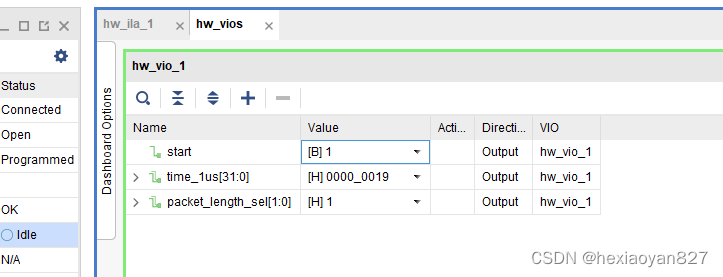

FPGA端VIO配置:

Start:控制开始发送,结束发送。

packet_length_sel:可以选择UDP包长:0是1024字节,1是2048字节,2是4096字节,3是8192字节。

time_1us:可以配置发送间隔,以1US为单位作为间隔,默认值为1000_000,即为1s钟间隔。

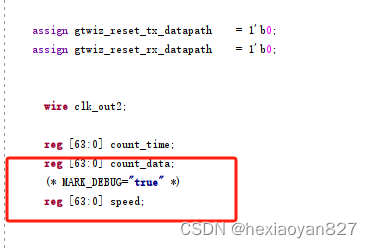

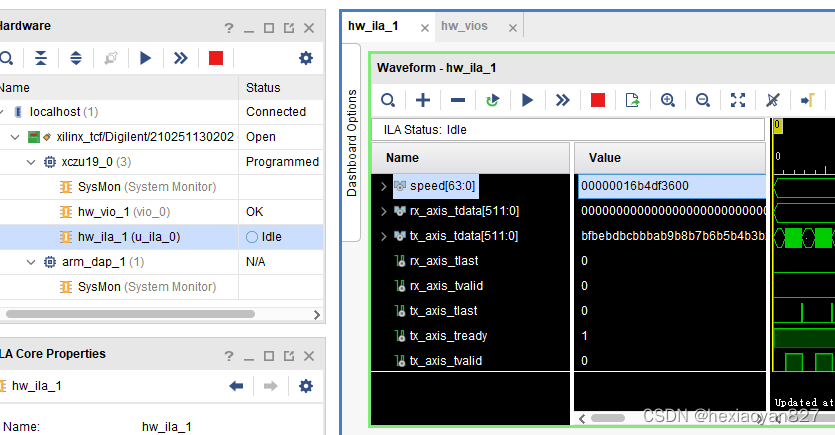

FPGA端发送接收速率显示是speed信号,ila在线观测,在代码中位置:

100G UDP产生模块:

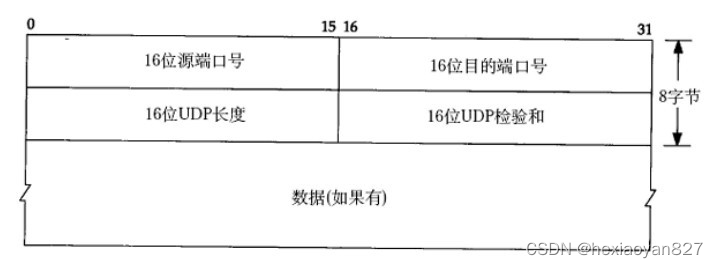

- UDP格式说明如下图:

下面分析一帧基于UDP的TFTP协议帧。

以太网首部

0000: 00 05 5d 67 d0 b1 00 05 5d 61 58 a8 08 00

IP首部

0000:?????????????????????????????????????????? 45 00

0010: 00 53 93 25 00 00 80 11 25 ec c0 a8 00 37 c0 a8

0020: 00 01

UDP首部

0020:????? 05 d4 00 45 00 3f ac 40

TFTP协议

0020:?????????????????????????????? 00 01 'c'':''\''q'

0030: 'w''e''r''q''.''q''w''e'00 'n''e''t''a''s''c''i'

0040: 'i'00 'b''l''k''s''i''z''e'00 '5''1''2'00 't''i'

0050: 'm''e''o''u''t'00 '1''0'00 't''s''i''z''e'00 '0'

0060: 00

以太网首部:源MAC地址是00:05:5d:61:58:a8,目的MAC地址是00:05:5d:67:d0:b1,上层协议类型0x0800表示IP。

IP首部:每一个字节0x45包含4位版本号和4位首部长度,版本号为4,即IPv4,首部长度为5,说明IP首部不带有选项字段。服务类型为0,没有使用服务。16位总长度字段(包括IP首部和IP层payload的长度)为0x0053,即83字节,加上以太网首部14字节可知整个帧长度是97字节。IP报标识是0x9325,标志字段和片偏移字段设置为0x0000,就是DF=0允许分片,MF=0此数据报没有更多分片,没有分片偏移。TTL是0x80,也就是128。上层协议0x11表示UDP协议。IP首部校验和为0x25ec,源主机IP是c0 a8 00 37(192.168.0.55),目的主机IP是c0 a8 00 01(192.168.0.1)。

UDP首部:源端口号0x05d4(1492)是客户端的端口号,目的端口号0x0045(69)是TFTP服务的well-known端口号。UDP报长度为0x003f,即63字节,包括UDP首部和UDP层payload的长度。UDP首部和UDP层payload的校验和为0xac40。

cmac 配置按照example中的配置进行配置。

- ConnectX6 100G网卡DPDK方案

dpdk 全称data plane development kit(数据平面转发工具),为 Intel 处理器架构下用户空间高效的数据包处理提供了库函数和驱动的支持,数据包的控制层和数据层分开,dpdk绕过linux内核协议栈将数据包的接受处理放到应用层。

DPDK拦截中断,不触发后续中断流程,并绕过协议栈,通过UIO技术将网卡收到的报文拷贝到应用层处理,报文不再经过内核协议栈。减少了中断,DPDK的包全部在用户控件使用内存池管理,内核控件与用户空间的内存交互不用进行拷贝,只做控制权转移,减少报文拷贝过程,提高报文的转发效率。

操作系统 :ubuntu20.04

网卡: Mellanox CX6 100G

DPDK:20.11

- 测试

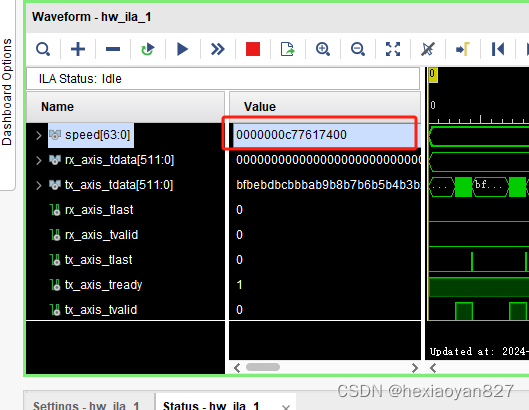

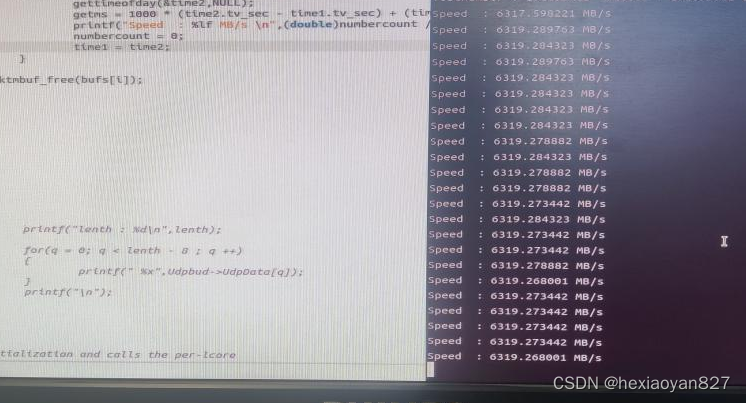

Vivado VIO设置:包间隔设置30us、UDP包大小设置1024字节

当前FPGA统计发送速度:0xc77617400 ?十进制 53 542 482 944

PC接收数据:无丢包

提升速度测试:

速率统计:0x16B4DF3AAA ?十进制:97 523 808 938

总效率为总带宽90%以上。只开启当前接收软件情况下,总体算稳定。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!