《PCI Express体系结构导读》随记 —— 第I篇 第1章 PCI总线的基本知识(3)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第1章 PCI总线的基本知识(2)

1.1 PCI总线的组成

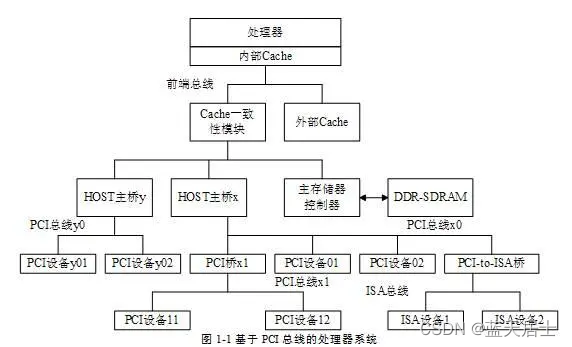

如前文所述,PCI总线作为处理器系统的本地总线,是处理器系统的一个组成部件。因此,讲述PCI总线的组成结构,不能离开处理器系统这个大环境。在一个处理器系统中,与PCI总线相关的模块如下图所示:

图中PCI总线相关的模块包括:HOST主桥、PCI总线、PCI桥和PCI设备。PCI总线由HOST主桥和PCI桥推出,HOST主桥和主存储器控制器在同一级总线上,因此PCI设备可以方便地通过HOST主桥访问主存储器,即进行DMA操作。

值得注意的是,PCI设备的DMA操作需要与处理器系统的Cache进行一致性操作。当PCI设备通过HOST主桥访问主存储器时,Cache一致性模块将进行地址监听,并根据监听的结果改变Cache的状态。

在一些简单的处理器系统中,可能不含有PCI桥,此时所有PCI设备都是连接在HOST主桥推出的PCI总线上。此外,在一些处理器系统中可能含有多个HOST主桥,如上图所示的处理器系统中含有HOST主桥x和HOST主桥y。

1.1.1 HOST主桥

HOST主桥是一个很特别的芯片,其主要功能是隔离外处理器系统的存储器域与处理器系统的PCI总线域,管理PCI总线域,并完成处理器与PCI设备间的数据交换。处理器与PCI设备间的数据交换主要由“处理器访问PCI设备的地址空间”和“PCI设备使用DMA机制访问主存储器”这两部分组成。

为简便起见,下面将处理器系统的存储器简称为存储器域,而将处理器系统的PCI总线域称为PCI总线域。值得注意的是,在一个处理器系统中,有几个HOST主桥,就有几个PCI总线域。

HOST主桥在处理器系统中的位置并不相同,如PowerPC处理器将HOST主桥与处理器集成到一个芯片中。而有些处理器不进行这种集成,如x86处理器使用南北桥结构,处理器内核在一个芯片中,而HOST主桥在北桥中。但是从处理器体系结构的角度来看,这些集成方式并不重要。

前文已提到,PCI设备通过HOST主桥访问主存储器时,需要与处理器的Cache进行一致性操作,因此在设计HOST主桥时,需要考虑Cache一致性操作。在HOST主桥中,还含有许多数据缓冲,以支持PCI总线的预读机制。

HOST主桥是联系处理器与PCI设备的桥梁。在一个处理器系统中,每一个HOST主桥都管理了一棵PCI总线树,在同一棵PCI总线树上的所有PCI设备属于同一个PCI总线域。如上图所示,HOST主桥x之下的PCI设备属于PCI总线x域,而HOST主桥y之下的PCI设备属于PCI总线y域。在这棵总线树上的所有PCI设备的配置空间,都由HOST主桥通过配置读写总线周期访问。

如果HOST主桥支持PCI V3.0规范的Peer-to-Peer数据传送方式,那么分属于不同PCI总线域的PCI设备可以直接进行数据交换。如上图所示,如果HOST主桥y支持Peer-to-Peer数据传送方式,PCI设备y01可以直接访问PCI设备01或者PCI设备11,而不需要处理器的参与。但是这种跨越总线域的数据传送方式在PC架构中并不常用,在PC架构中,重点考虑的是PCI设备与主存储器之间的数据交换,而非PCI设备之间的数据交换。此外在PC架构中,具有两个HOST主桥的处理器系统也并不多见。

在PowerPC处理器中,HOST主桥可以通过设置Inbound寄存器,使得分属于不同PCI总线域的设备可以直接通信。许多PowerPC处理器都具有多个HOST主桥。

更多内容请看下回。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!