关于FPGA仿真复位信号和实际板子复位信号的吐血大坑

2024-01-08 19:51:02

最近在研究mipi dphy IP下载到板子上进行验证的初步流程问题

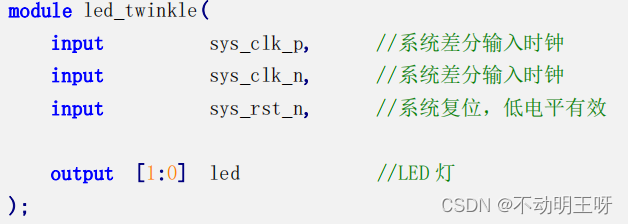

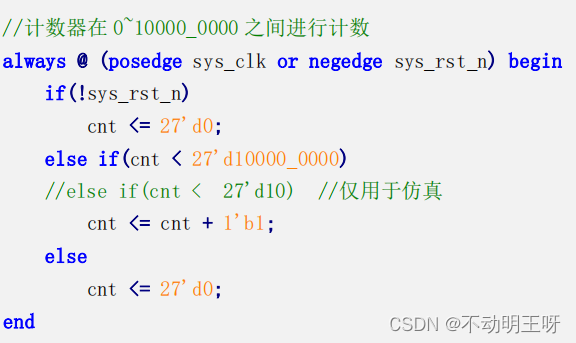

IP的example案例里面,系统复位全是高电平复位,低电平工作

想当然的打通IP流程,写工程的时候也使用了高电平复位,低电平复位

结果调试了N轮,init_done信号一直没有拉高。

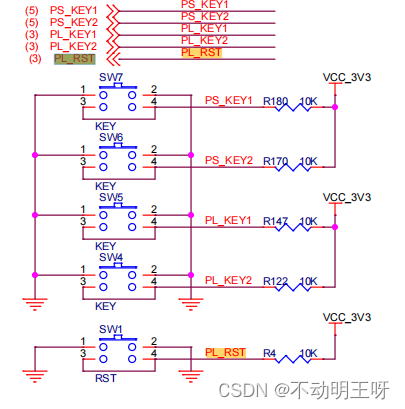

后来查询了电路图,发现是高电平工作,低电平复位

再重新看例程,是低电平复位,吐血!!!

记录一下

FPGA例程仿真没问题,下载到板子出错,因素之一可能是复位信号不一样。

文章来源:https://blog.csdn.net/qq_36683398/article/details/135462928

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!