复旦微在线调试DDR

模式介绍

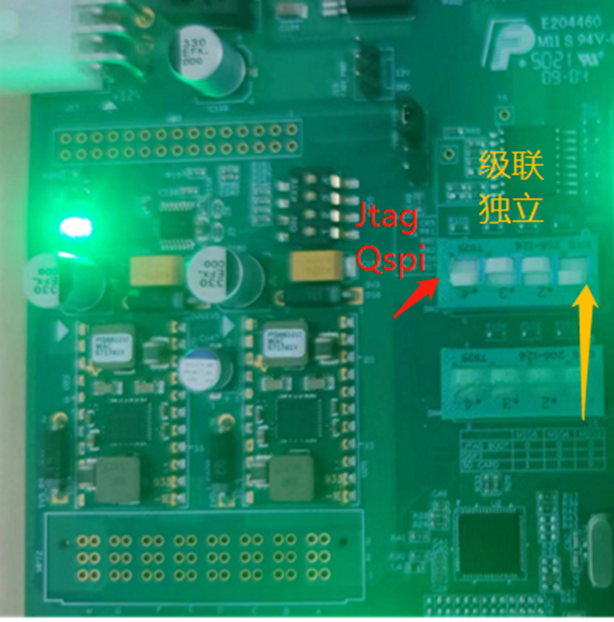

Jtag模式

Jtag模式用于在线调试,烧写,红色箭头所示拨码开关,拨上为jtag模式

Qspi模式

Qspi模式用于独立运行,红色箭头所示拨码开关,拨下为Qspi模式

级联模式

当PL侧代码不用修改时可以用级联模式,jtag烧写器直接插到开发板上。

黄色箭头所示拨码开关拨上为级联

独立模式

PS和PL都要接仿真器联调时用独立模式,PS的JTAG接到飞线处

黄色箭头所示拨码开关拨上为独立

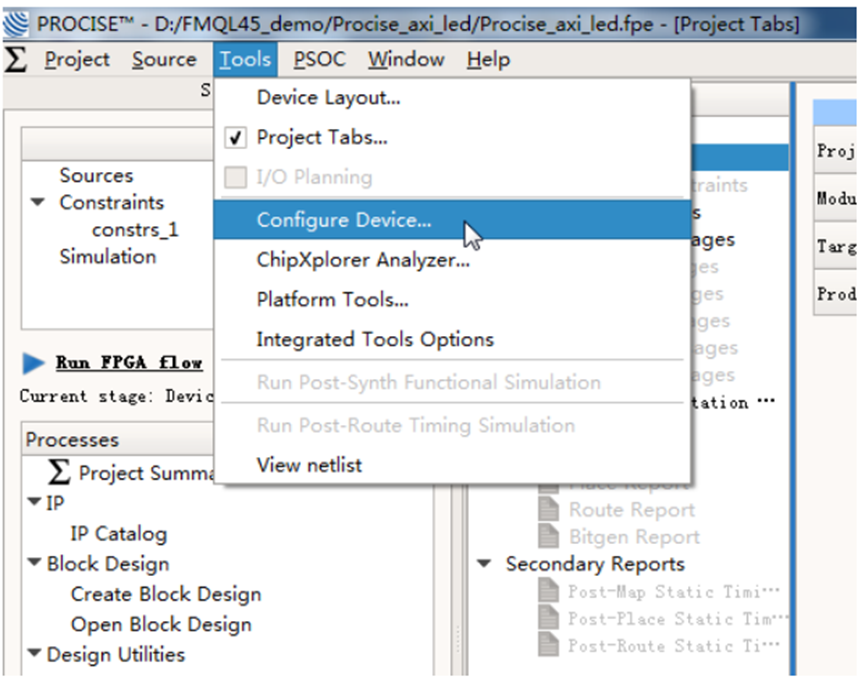

级联模式:

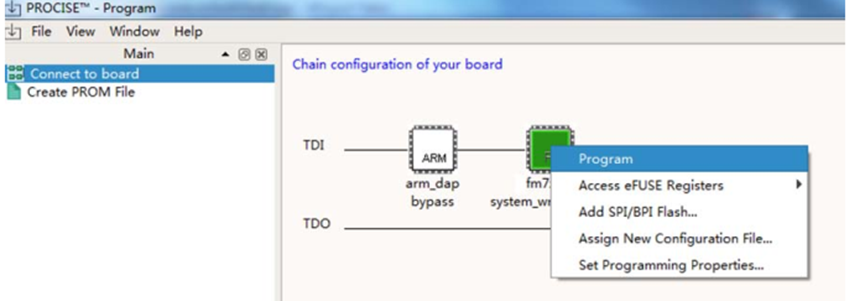

Procise 中选择 Tools->ConfigureDevice

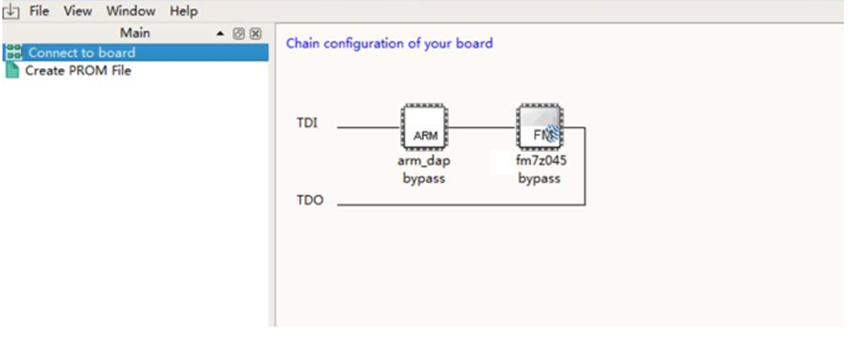

双击 Connect to board,连上开发板

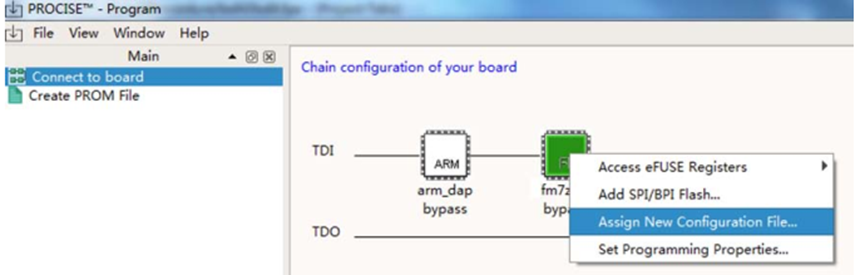

右键单击 fm7z045,选择 Assign New Configuration File

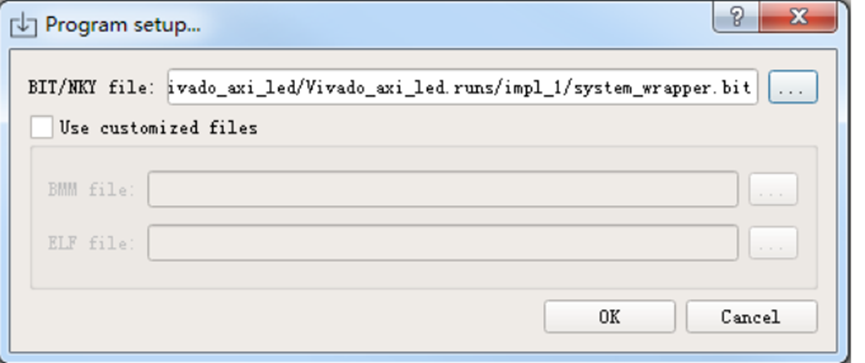

添加 正确的bit 文件

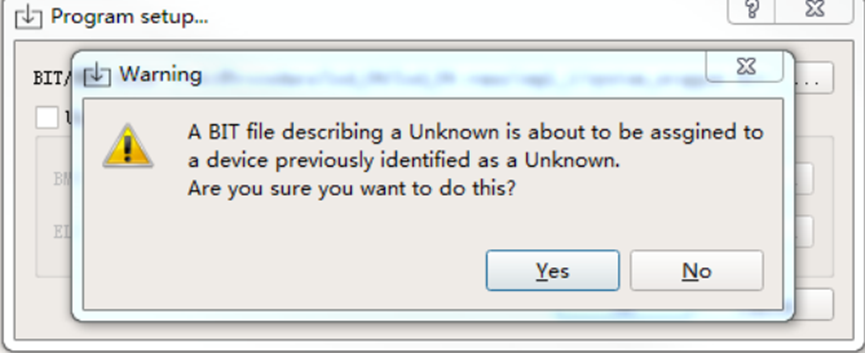

点击 Yes

右键单击 fm7z045,点击 Program 下载位流。 PL 部分设置成功

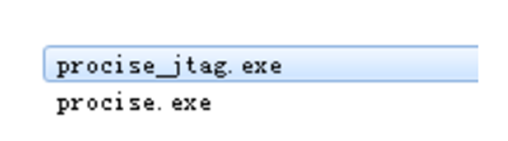

在任务管理器中找到 procise_jtag.exe,结束此进程。(否则 IAR_SDK 会识别不到 JTAG)

独立模式

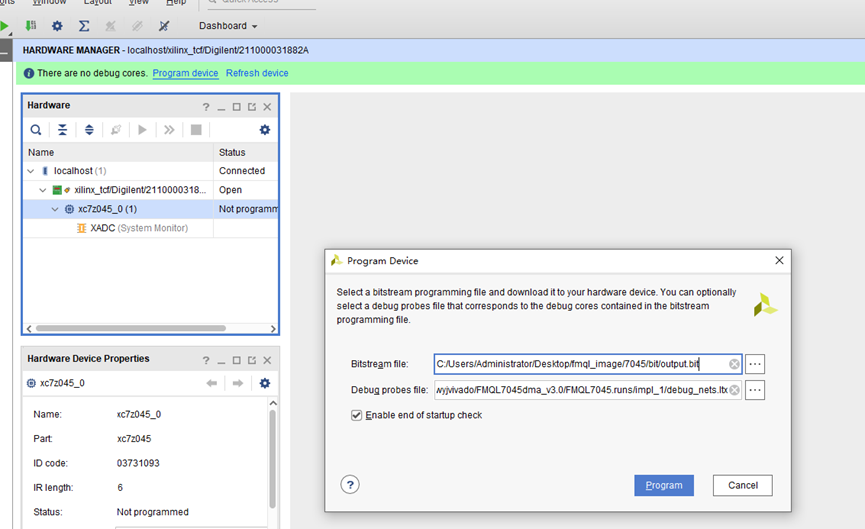

独立模式下省去上述步骤,由PL侧烧写bit文件后执行下列步骤

(PL侧正常使用Vivado烧写)

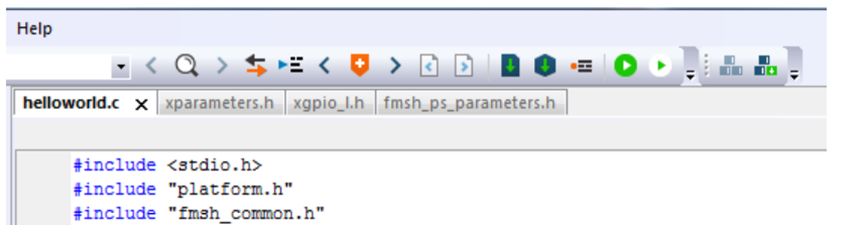

在 IAR_SDK 中,点击上方的绿色小箭头, Download and Debug

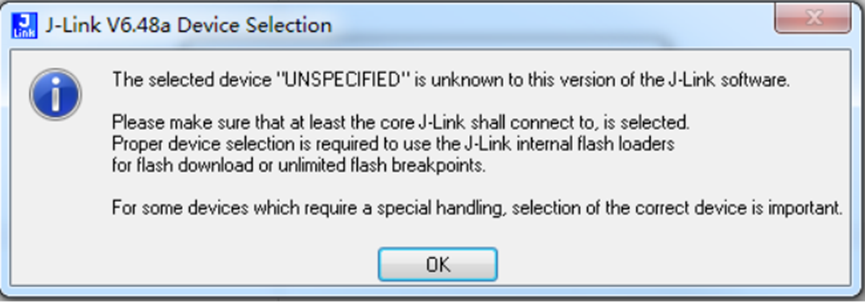

如果弹出提示,点击 OK

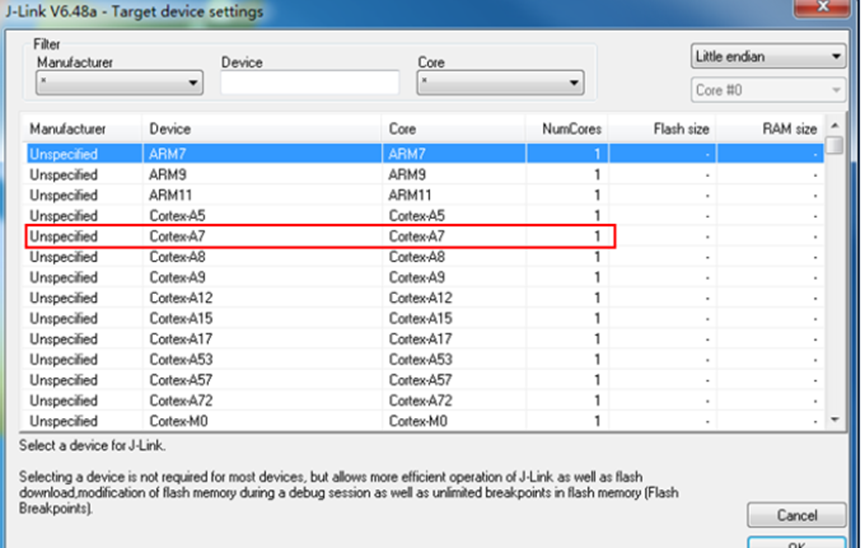

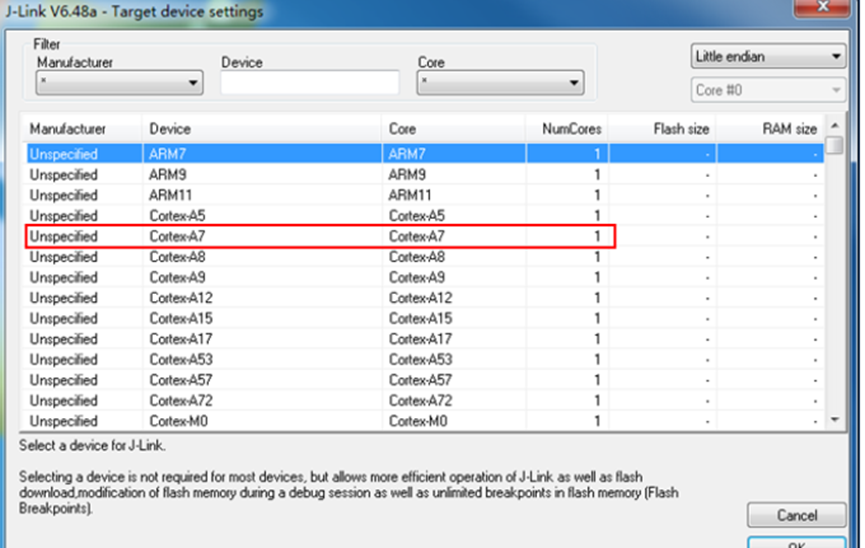

选择 Cortex-A7,点击 OK

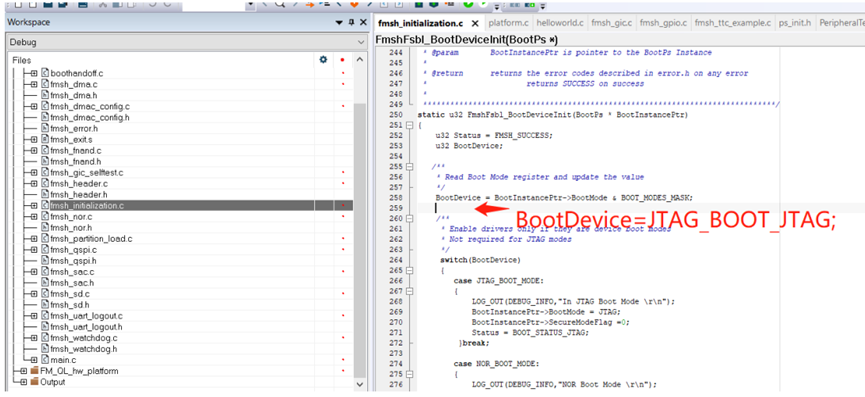

设置 fsbl 工程为 active(直接点击到 fsbl 工程就不需要这个操作),下载运行fsbl,在下图位置打上断点,断点只要在执行 ps_init 之后都可以。

运行到断点处,关闭 fsbl 调试界面:

退出调试界面后面, 特别注意的是 IAR 打断点退出 debug 还会继续往前运行的,这个是 IAR 的 bug, 在线调试的话,如果硬件板子不好修改 boot mode 的跳线的话,即 MIO5 从高变低(qspi falsh 启动模式切到 jtag 启动模式)可以直接把用来初始化 DDR的 fsbl 的强制修改为 jtag 启动,这样的话这个 fsbl 也就不会去 qspi 加载后续镜像了,特别是可以避免 qspi 里的程序有问题会导致 cpu 挂死等问题导致 jlink 断链

退出调试,切换到helloworld工程再次调试即可

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!