FPGA的MARK_DEBUG调试之波形抓取

一、描述

????????在工作时发现FPGA向ARM传输的数据有问题,因此想抓取一下FPGA的波形。作为传统方式使用示波器抓取过于麻烦,因此使用VIVADO自带的DEBUG功能抓取输出的数据波形。

先上几个比较好的学习链接:

https://www.cnblogs.com/tubujia/p/9242895.html

二、实现步骤

2.1、添加(*MARK_DEBUG="true"*)

? ? ? ? 在调试需要调试的信号前加入MARK标志点,要注意在添加MARK点

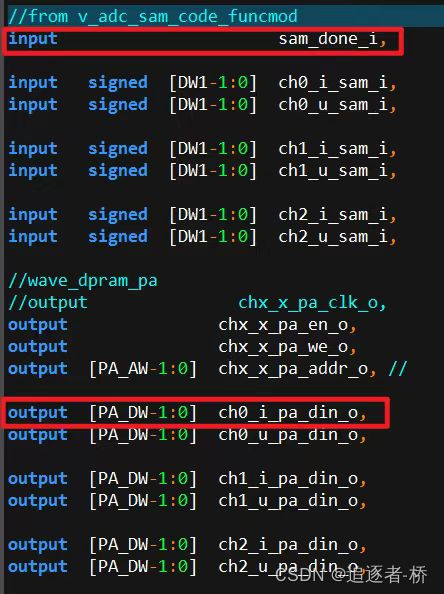

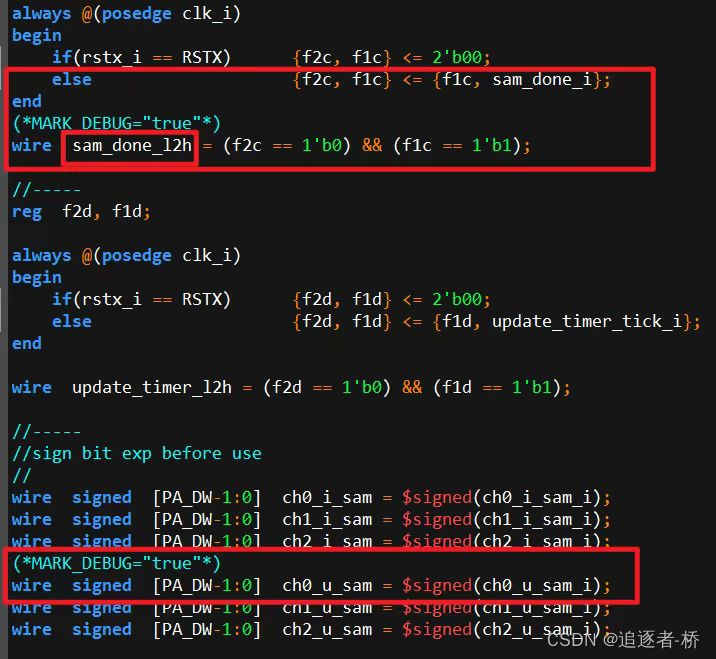

注意:一定要把该信号的触发信号也加入,MARK点不能加在input、output上,只能加在wire、reg信号上进行抓取。

如图所示:

当我想要查看input和output信号时,并不会在input和ouput前面加入MARK点,而是加载与之相连结的wire或者reg量上。

在想观测的信号上,添加好MARK_DEBUG后进行保存。

2.2、Set Up Debug

? ? ? ? ? 添加好mark点后进行,RTL代码编译,然后进行Synthesis综合。使用Synthesis综合工具中的Set?Up?Debug进行信号的添加,添加时注意其时钟。

添加调试设置:两个启动条件打上对(网上很多文档和教学视频上并没有管,后期会有影响)

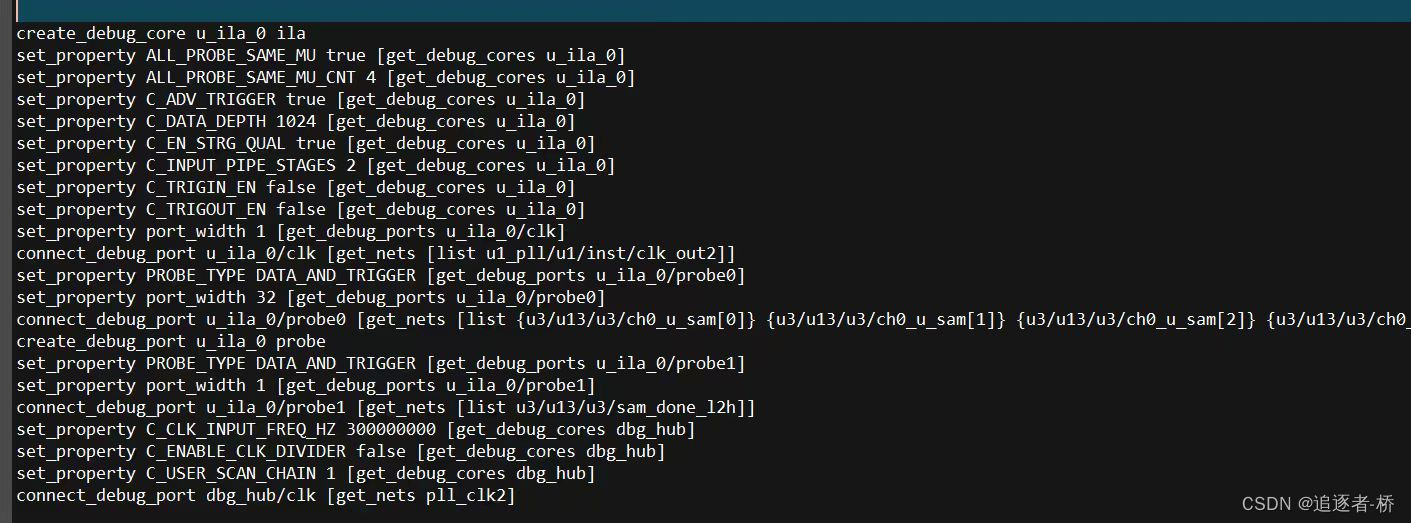

然后点击下一步进入Set up Debug?Summary界面预览,点击完成就可以将MARK信号进行添加了。Ctrl+S进行保存,会自动在XDC文件中添加debug_core:ila调试IP核,同时会添加信号以及相应的时钟信息,增加probe探针连接检测信号。

以上DEBUG已经加入完成,是不是很简单,但是从不会到完成的时候还是挺曲折的。?

2.3、bit/bin流文件生成

? ? ? ? 首先通过Implementayion进行代码的实现,实现完成后生成bit文件,这一步很简单就不细说了,下面以bit文件进行调试,(bit文件会烧录到FPGA的ram中,掉电会自动清除;bin文件会存储到flash中掉电不会清除)。

2.4、下载程序

在下载bit流文件时,需要同时下载debug_net.ltx约束文件

2.5、调试

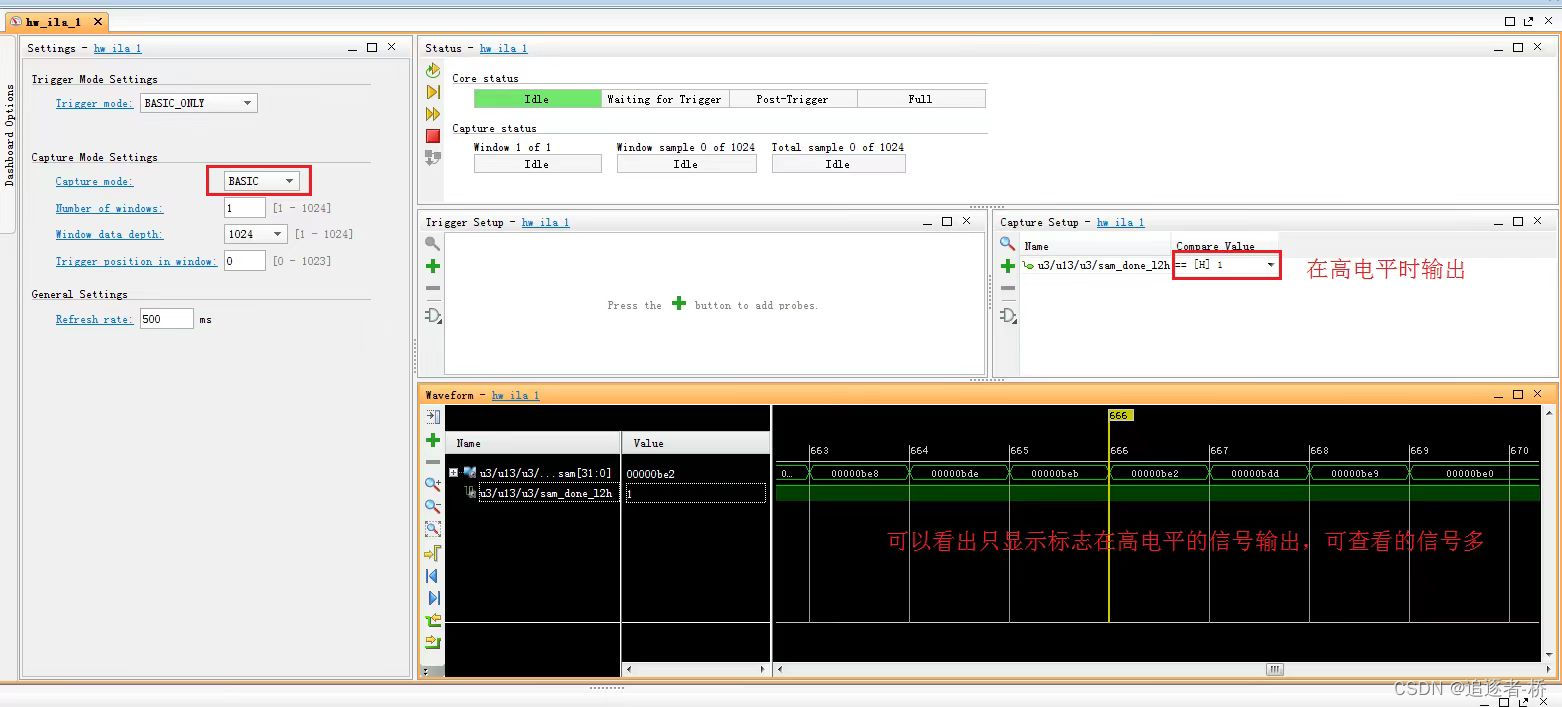

下载好程序后会进入调试界面:

点击调试运行,可以看出出发信号在高低电平之间切换,但是对于所监控的信号来说低电平是并不想要监控到的,因此需要选择触发方式,若在2.2不设置启动条件,则是无法选择的。

选择出发条件,在触发信号为高电平时输出:

可以看到调试显示的波形一直是出发信号为高点评的状态,能更多的监控到波形数据。

同时可以设置查看方式,来查看其波形

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!