FPGA时序分析与约束(5)——时序路径

一、前言

? ? ? ? 在之前的文章中我们分别介绍了组合电路的时序,时序电路的时序和时钟的时序问题,我们也对于时序分析,时序约束和时序收敛几个基本概念进行了区分,在这篇文章中,我们将介绍时序约束相关的最后一部分基本概念,带领大家了解什么是时序路径。

二、常用术语

????????时序分析中的常用术语:

- 源时钟(Source Clock/Launch Clock,也称为发起时钟)

- 目的时钟(Destination Clock/Capture Clock,也称为捕获时钟)

- 发起沿(launch edge,源时钟产生数据的有效时钟沿)

- 捕获沿(capture edge,目的时钟捕获数据的有效时钟沿)

- 发起沿通常在0ns,捕获沿通常在下一个发起沿,发起沿和捕获沿通常相差一个时钟周期。

?三、时序路径

? ? ? ? 时序路径指的是信号可以继续穿过,不必等待其他触发条件的路径。沿着时序路径,信号仅仅在通过电路元器件时有延迟。

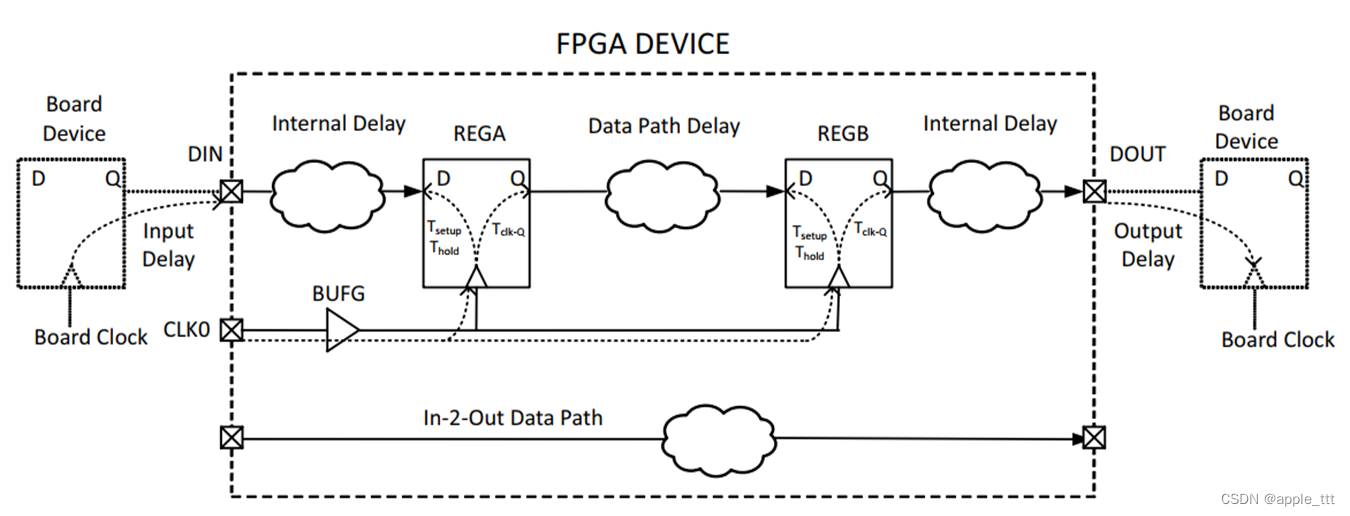

1、起点和终点

? ? ? ? 信号时序开始的点称为起点。因此,对于给定电路,所有输入都可以作为起点。信号必须被定时的点称为终点。因此,所有输出都可以作为终点。

? ? ? ? 在寄存器中,输入D必须等待时钟触发的到达。所以,直到D到达才能完成的过渡过程现在必须等待。现在进一步传递信号的时序将取决于时钟的达到时间。此处D应检查是否满足建立时间和保持时间。因此,时序路径在此结束。所以,寄存器也可以作为终点。

? ? ? ? 类似地,寄存器也可以作为起点。信号将从寄存器地Q引脚开始,然后向前传递。严格来说,时序从时钟源开始,然后到达触发器地clock引脚,接着进入触发器的Q引脚,然后继续向前。所以,严格来说,寄存器不是真正的起点。但是,大部分实际使用中,我们还是把寄存器称之为起点,但是在实际分析中,路径追踪是从时钟源开始的。

2、一条普通时序路径的三要素

1.1 源时钟路径

????????从源时钟的源节点(通常是FPGA的时钟输入引脚)到源寄存器的时钟端口的路径。当时序路径的起点是FPGA输入端口时,该时序路径是没有源时钟路径的。

1.2 数据路径

????????从时序路径的起点到时序路径的终点之间的数据传播路径。时序路径的起点可以是源寄存器的时钟端口或FPGA的输入端口,时序路径的终点可以是目的寄存器的输入端口或FPGA的输出端口。

1.3 目的时钟路径????????

????????从目的时钟的源节点(通常是FPGA的时钟输入引脚)到目的寄存器的时钟端口的路径。当时序路径的终点是FPGA的输出端口时,该时序路径是没有目的时钟路径的。

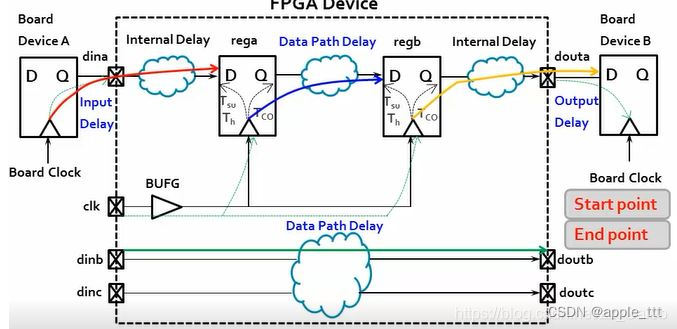

3、FPGA中常见的4种时序路径

?????????一般来说,FPGA中的时序路径可以分化成4种不同的类型

(1)第一类时序路径(红色):从device A的时钟到FPGA的第一级寄存器的输入端口。

(2)第二类时序路径(蓝色):两个同步元件之间的路径(rega到regb)

(3)第三类时序路径(黄色):最后一级寄存器到device B数据端口的路径

(4)第四类时序路径(绿色):端口到端口的路径(dinb到doutb)

2.1 引脚到寄存器(从FPGA的输入端口到目的寄存器的数据输入端口)

- 数据由Board clock发起并在FPGA外部产生;

- 数据经过Input Delay的延迟后到达FPGA的输入端口;

- 数据经过FPGA的Internal Delay后到达由目的时钟驱动的目的寄存器

- 这种路径是没有源时钟路径的,用户需要约束Input Delay和时钟来告知时序引擎必要信息,时序引擎才能正确的分析这种路径。

2.2 寄存器到寄存器(从源寄存器的时钟端口到目的寄存器的数据输入端口)

- 数据由源时钟发起并在FPGA内部产生;

- 数据经过Data Path Delay后到达由目的时钟驱动的目的寄存器;

- 这种时序路径是最常见的,用户需要约束源时钟和目的时钟告知时序引擎必要的信息,时序引擎才能正确的分析这种时序路径。

2.3 寄存器到引脚(从源寄存器的时钟端口到FPGA的输出端口)?

- 数据由源时钟发起并在FPGA内部产生;

- 数据经过Internal Delay后到达输出端口;

- 数据经过Output Delay后被Board Clock捕获到;

- 这种路径是没有目的时钟路径的,用户需要约束Output Delay和时钟来告知时序引擎必要信息,时序引擎才能正确的分析这种路径。

2.4 引脚到引脚(从FPGA的输入端口到FPGA的输出端口)

- 数据横穿FPGA,没有经过任何触发器,这种路径也叫in-to-out path,约束输入和输出延时的参考时钟可以使用虚拟时钟。

- 这种路径中只有数据路径,用户需要约束Input Delay和Output Delay,告知时序引擎必要的信息,时序引擎才能正确的分析这种时序路径。

四、总结

? ? ? ? 在本文中,我们主要介绍了时序分析过程中时序路径的基本概念,分别介绍了FPGA中常见的4种时序路径:(1)引脚到寄存器(从FPGA的输入端口到目的寄存器的数据输入端口)(2)寄存器到寄存器(从源寄存器的时钟端口到目的寄存器的数据输入端口)(3)寄存器到引脚(从源寄存器的时钟端口到FPGA的输出端口)?(4)引脚到引脚(从FPGA的输入端口到FPGA的输出端口)。这部分的内容是我们进行后续时序分析及时序约束的重要基础。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!