CPU 大小端模式(Endianness)

CPU 大小端模式(Endianness)是指在存储和处理多字节数据时,字节的顺序是如何排列的。它涉及到字节在内存中的存储方式以及读取和解释这些字节的顺序。

有两种常见的大小端模式:

-

大端模式(Big Endian):在大端模式下,高位字节(Most Significant Byte,MSB)存储在低地址,而低位字节(Least Significant Byte,LSB)存储在高地址。这意味着对于一个多字节数据,它的最高有效字节(Most Significant Byte)在内存中的地址较低,而最低有效字节(Least Significant Byte)在内存中的地址较高。

例如,对于十六进制数

0x12345678,在大端模式下它在内存中的表示为:12 34 56 78。 -

小端模式(Little Endian):在小端模式下,高位字节(Most Significant Byte,MSB)存储在高地址,而低位字节(Least Significant Byte,LSB)存储在低地址。这意味着对于一个多字节数据,它的最高有效字节(Most Significant Byte)在内存中的地址较高,而最低有效字节(Least Significant Byte)在内存中的地址较低。

例如,对于十六进制数

0x12345678,在小端模式下它在内存中的表示为:78 56 34 12。

在计算机系统中,CPU 的大小端模式由硬件设计决定,并且不同的体系结构有不同的默认模式。例如,x86 架构的 CPU 通常采用小端模式,而网络协议中常用的网络字节序采用的是大端模式。

大小端模式在数据传输、数据存储、网络通信、文件格式等方面都具有重要影响。在进行跨平台数据交换时,需要注意双方的大小端模式以确保数据的正确解释。

对于二进制数据,也存在大小端模式的概念。大小端模式不仅适用于多字节的十六进制数据,也适用于二进制数据的存储和解释。

对于二进制数据的大小端模式,可以将其视为多字节数据的一种特殊情况。在大端模式下,较高的位(Most Significant Bit,MSB)存储在较低的地址,而较低的位(Least Significant Bit,LSB)存储在较高的地址。而在小端模式下,较高的位(MSB)存储在较高的地址,而较低的位(LSB)存储在较低的地址。

举例来说,考虑一个8位的二进制数 10101010:

- 在大端模式下,它在内存中的表示为:

10101010,其中最高有效位(MSB)位于较低的地址,最低有效位(LSB)位于较高的地址。 - 在小端模式下,它在内存中的表示为:

01010101,其中最高有效位(MSB)位于较高的地址,最低有效位(LSB)位于较低的地址。

可以看出,大小端模式同样适用于二进制数据的存储和解释。

在处理二进制数据时,需要根据具体的大小端模式来解释和操作数据。例如,在网络通信中,常用的网络字节序采用的是大端模式,因此在进行网络数据传输时,需要将数据以大端模式进行编码和解码。

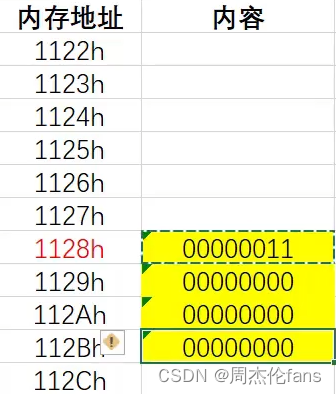

总而言之,小端模式就是从高地址位置开始往低地址读字节(比较低字节的放到地址比较低的位置)

00000000 00000000 00000000 00000011

大端模式就是从低地址位置开始往高地址读字节(比较低字节的放到地址比较高的位置)

00000011 00000000 00000000 00000000

大小端模式不仅适用于十六进制数据,也适用于二进制数据的存储和解释。在处理二进制数据时,需要根据具体的大小端模式来正确解释和操作数据。

需要注意的是,对于单个字节的数据,大小端模式没有影响,因为它只有一个字节,没有字节顺序可言。大小端模式只在多字节数据的存储和解释中才有意义。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!