verilog基础语法之比较器

逻辑运算符以及逻辑电路概述

逻辑运算符常用于条件判断语句,输出为布尔值True/False。逻辑运算符是基于比较器构造的。比较器电路是产生逻辑比较的本质;比较器电路的复杂度与位宽和比较类型相关;一般情况下可以先构造基本比较器,其他比较器由基本比较器合成。基本的比较器是>,==,<。其他逻辑运算符是由这三个基本比较器构造成的。>=比较器是由<比较器取反得到。!=比较器由==取反得到。<=比较器由>比较器取反得到。逻辑非比较器 !A≡(A==0)。逻辑与A&&B≡(A!=0)&(B!=0)。逻辑或A||B≡(A!=0)|(B!=0)。

逻辑运算符如下:

// The forllowing logical operators are used in conditional TRUE/FALSE statements

// such as an if statement in order to specify the condition for the operation.

//

// ! .... Not True

// && ... Both Inputs True

// || ... Either Input True

// == ... Inputs Equal

// === .. Inputs Equal including X and Z (simulation only)

// != ... Inputs Not Equal

// !== .. Inputs Not Equal including X and Z (simulation only)

// < .... Less-than

// <= ... Less-than or Equal

// > .... Greater-than

// >= ... Greater-than or Equal

目录:

1.大于比较器 >

2. 小于等于比较器 ≤

3. 小于比较器 <

4. 大于等于比较器 ≥

5. 等于比较器 ==

6. 不等于比较器 !=

7. 逻辑非 !

8. 逻辑与 &&

9. 逻辑或 ||

1.大于比较器 >

代码

module assign1(

input[3:0] a,b,

output y1

);

assign y1 = a>b; // 取出某一位

endmodule

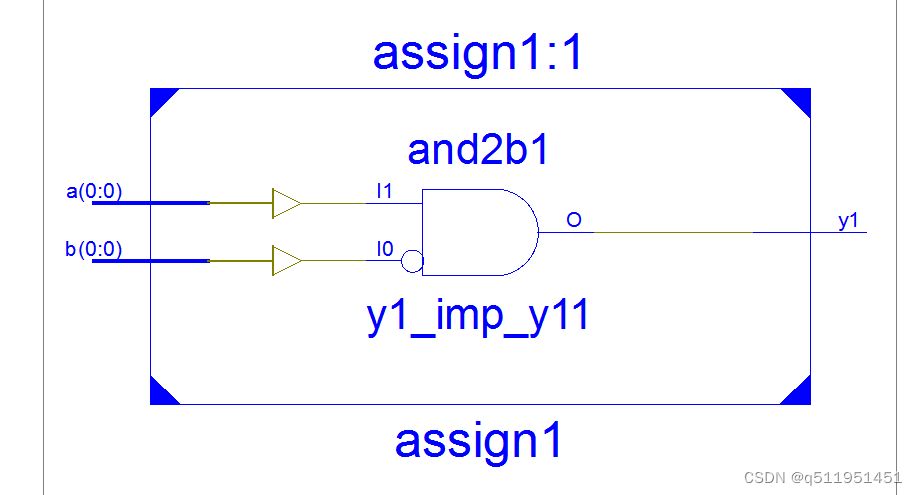

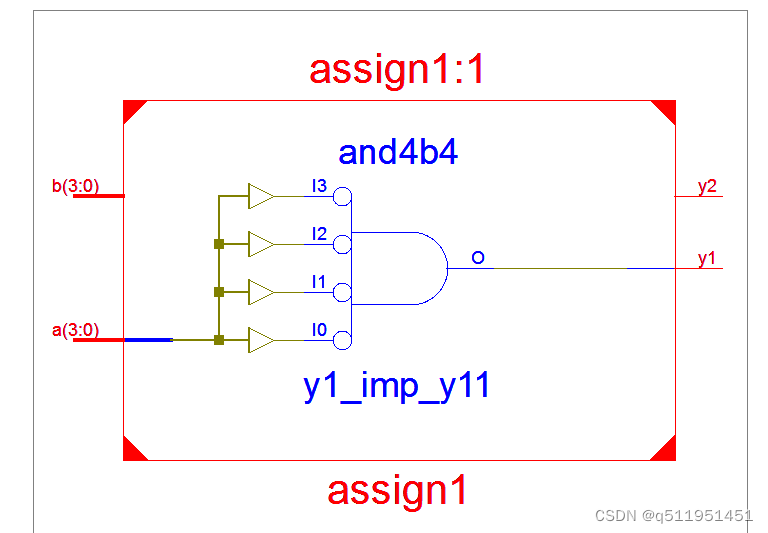

一位>RTL结构图,该逻辑仅仅是一个与门,其中a==1,b==0时,输出为高。

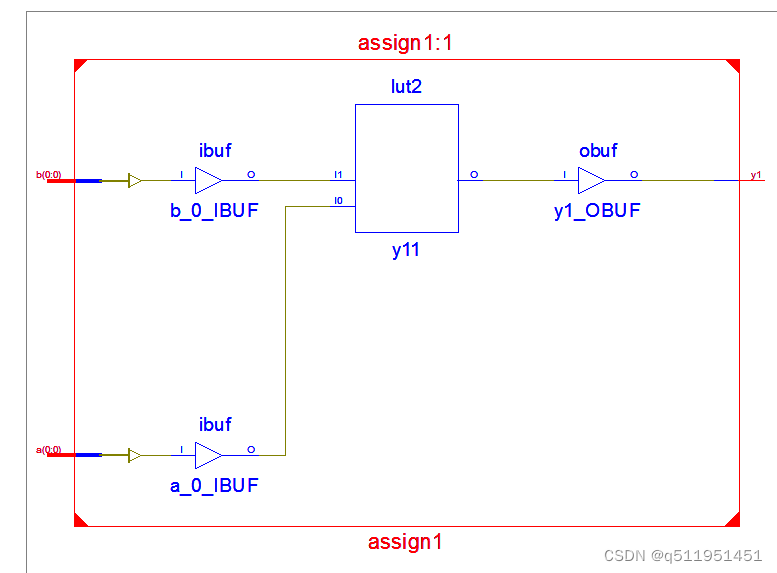

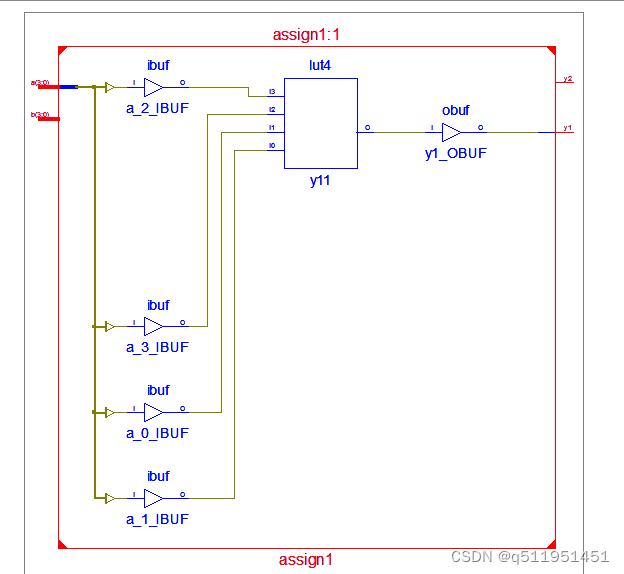

一位>技术原理图,一个与运算仅仅需要一个Lut查找表即可实现

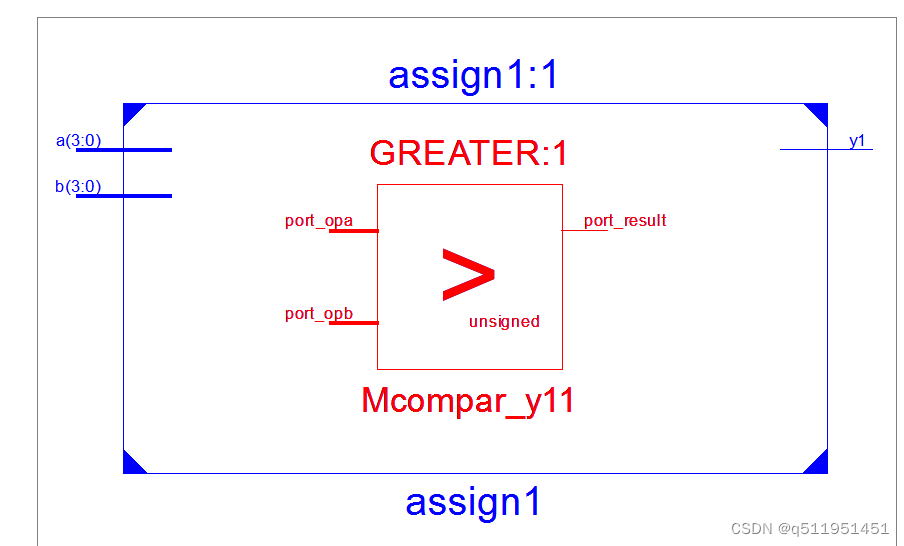

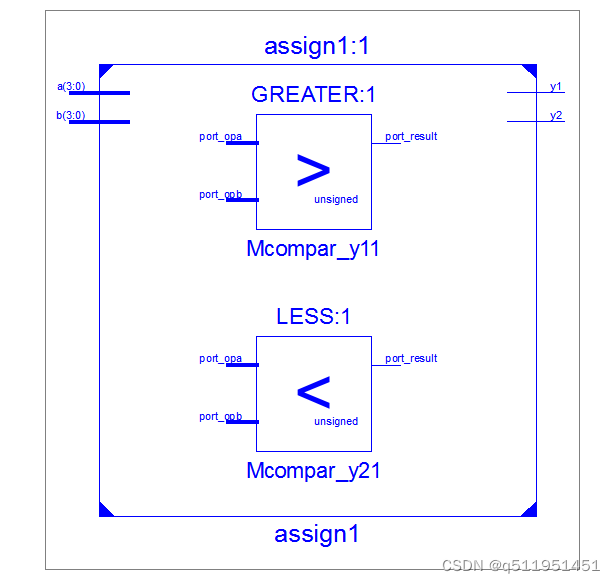

四位>比较器RTL结构图,标识出一个>模块,内部不可以观察。

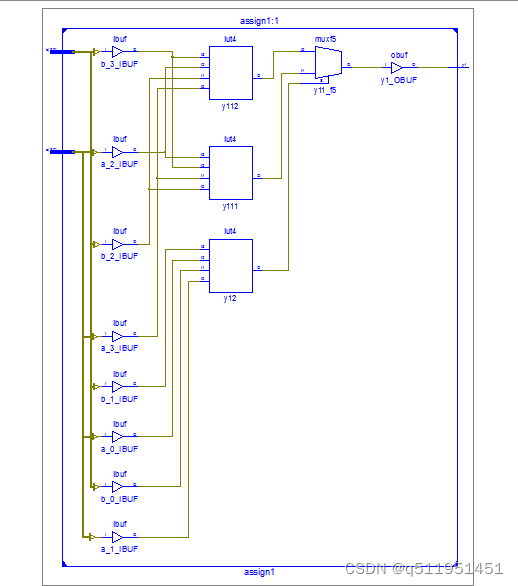

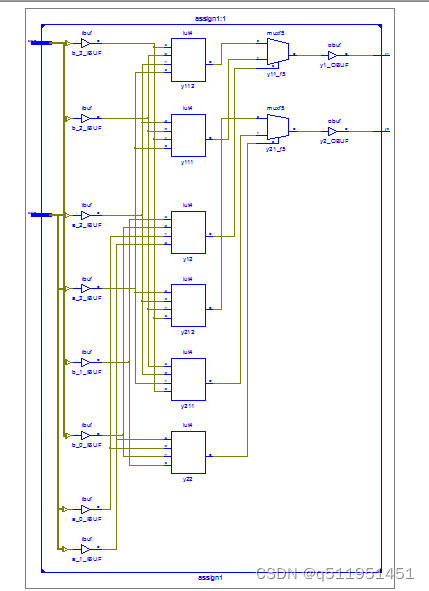

技术原理图,多位比较器本质上仍然是一个组合逻辑,通过lut+mux来实现。

2. 小于比较器 <

单独观察<比较器,就可以看成是>比较器换个输入端口即可实现。需要>与<比较器一起实现观察。

代码

// 18.<比较器基本电路

module assign1(

input[3:0] a,b,

output y1,

output y2

);

assign y1 = a>b; // 取出某一位

assign y2 = a<b; // 取出某一位

endmodule

RTL结构图,依然是一个封装模块。

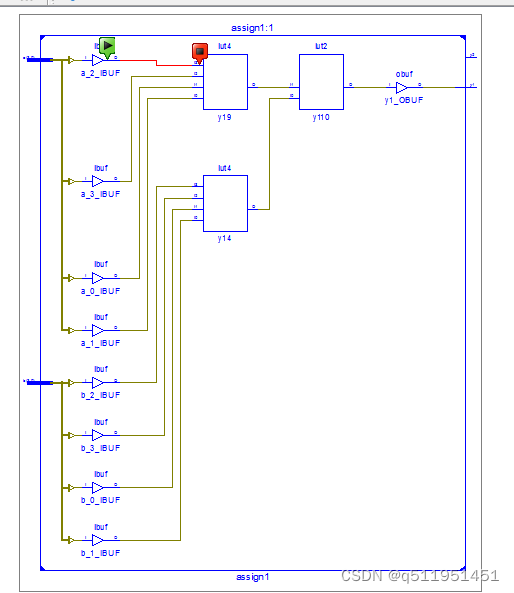

技术原理图,这是组合逻辑电路,

3. 小于等于比较器 ≤

代码

module assign1(

input[3:0] a,b,

output y1,

output y2

);

//assign y1 = a>b; // 取出某一位

assign y2 = a<=b; // 取出某一位

endmodule

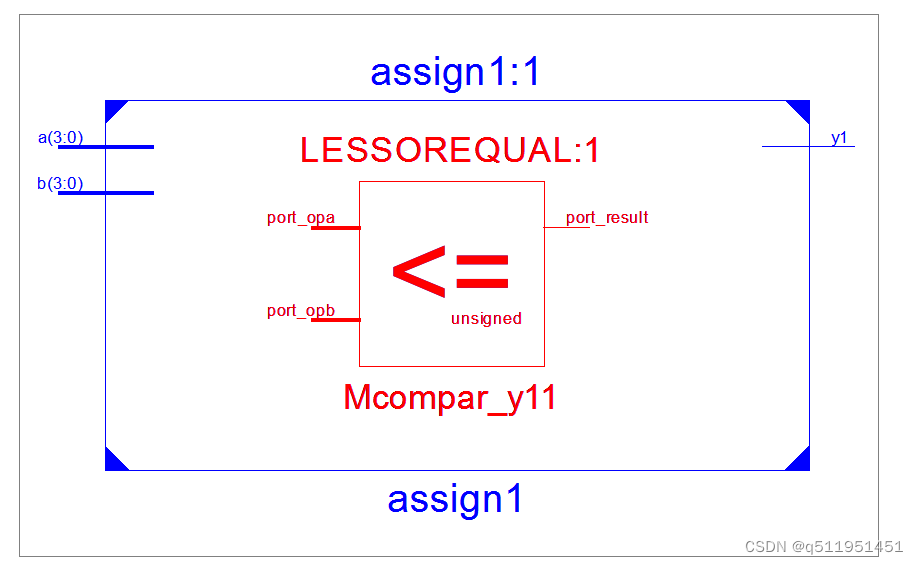

四位RTL结构图,该电路是一个封装模块,不可打开。

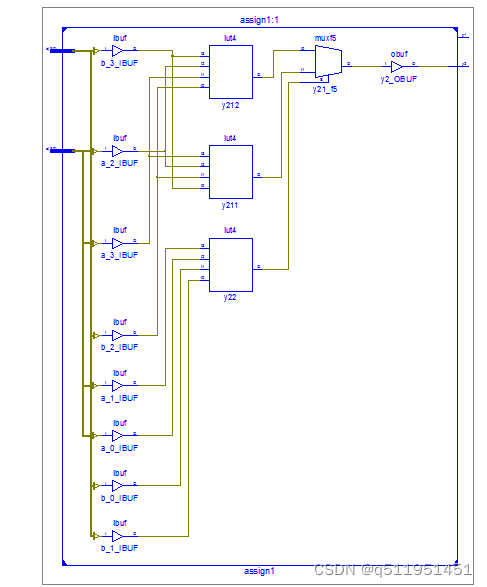

四位技术原理图,组合电路来实现

4. 大于等于比较器≥

单独观察≥比较器,它的本质也是把≤的输入端口修改一下,≥与≤一起观察。

代码

module assign1(

input[3:0] a,b,

output y1,

output y2

);

assign y1 = a>=b; // 取出某一位

assign y2 = a<=b; // 取出某一位

endmodule

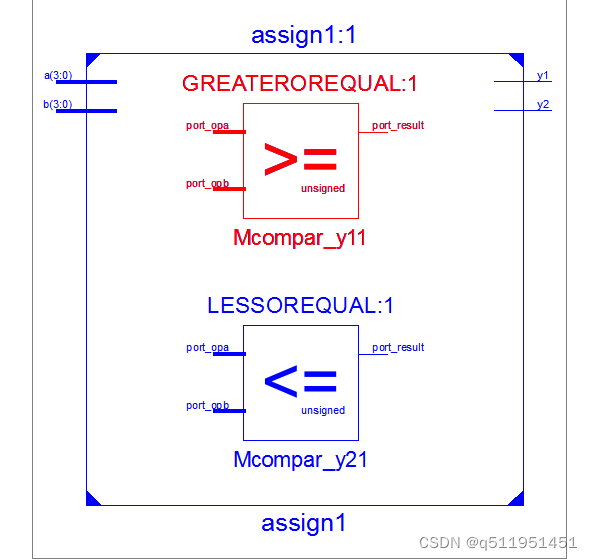

RTL结构图

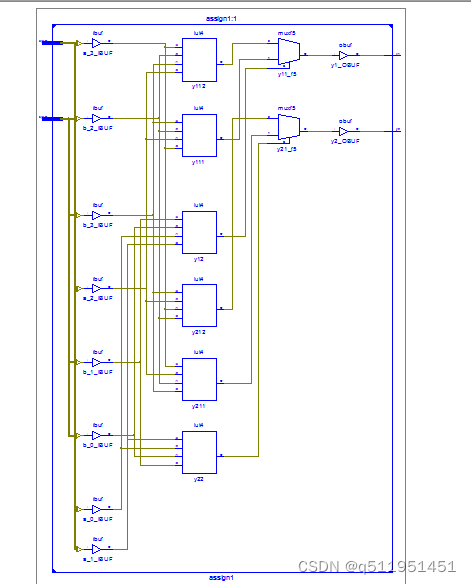

技术原理图

5. >,≥,<,≤综合电路图

代码

module assign1(

input[3:0] a,b,

output y1,

output y3,

output y4,

output y2

);

assign y1 = a>=b;

assign y2 = a<=b;

assign y3 = a>b;

assign y4 = a<b;

endmodule

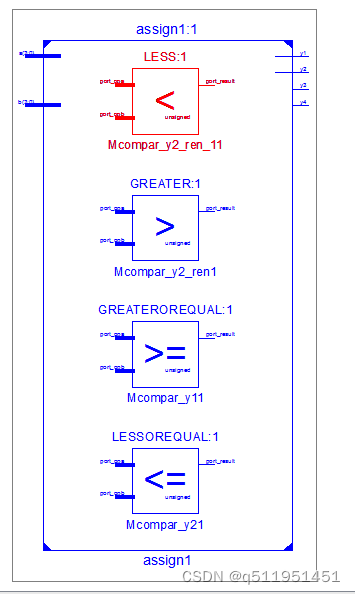

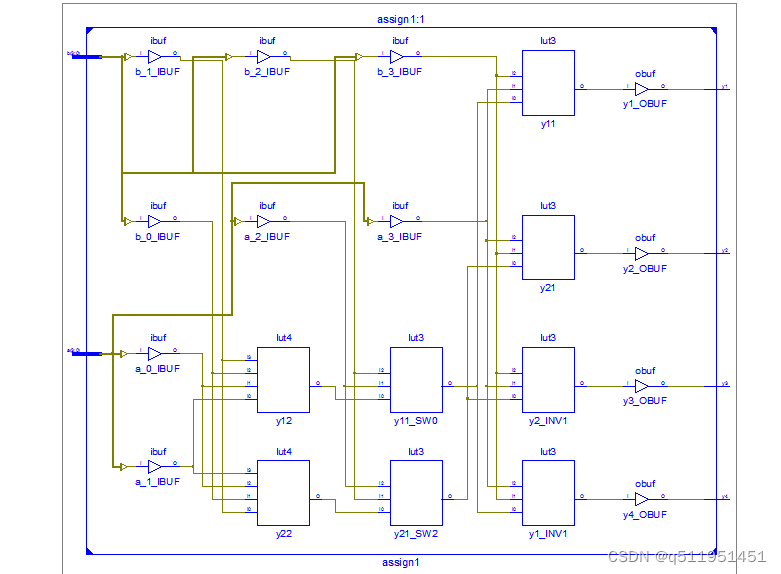

RTL结构图

技术原理图,从技术原理图来看,各个比较器相互独立,确保具有相同的门电路结构延时。并没有在基本的电路基础上取反来实现。这种方式消耗资源多,但是提高了比较器的响应速度。

6. 等于比较器 ==

代码

module assign1(

input[3:0] a,b,

output y1

);

assign y1 = a==b; // 取出某一位

endmodule

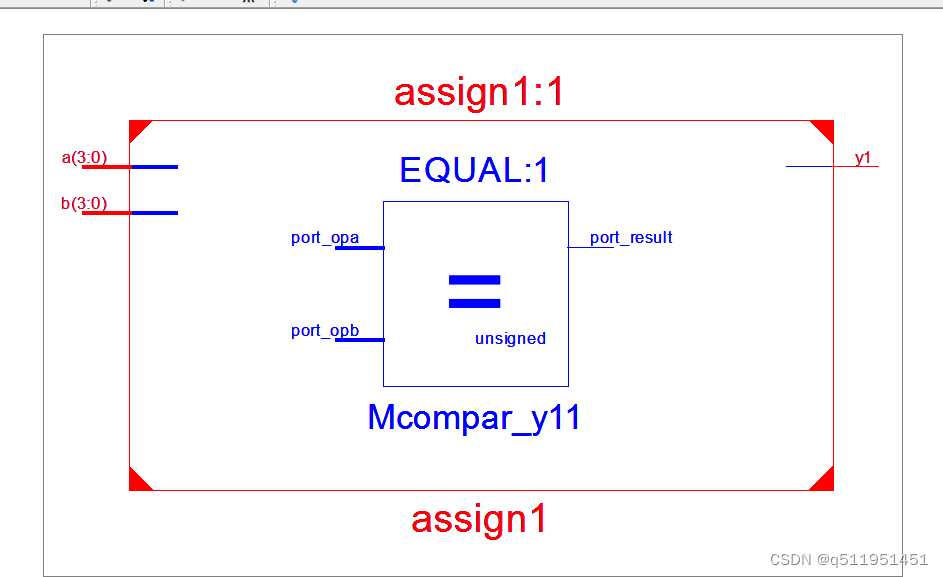

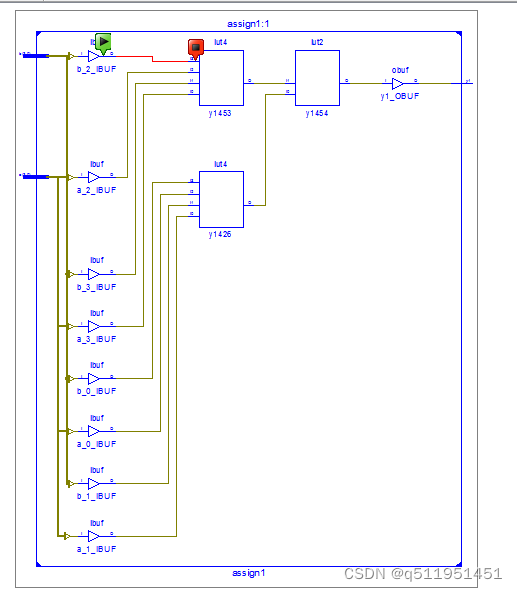

RTL结构图

技术原理图,技术原理图是组合逻辑

7. 等于比较器 !=

代码

module assign1(

input[3:0] a,b,

output y1

);

assign y1 = a!=b; // 取出某一位

endmodule

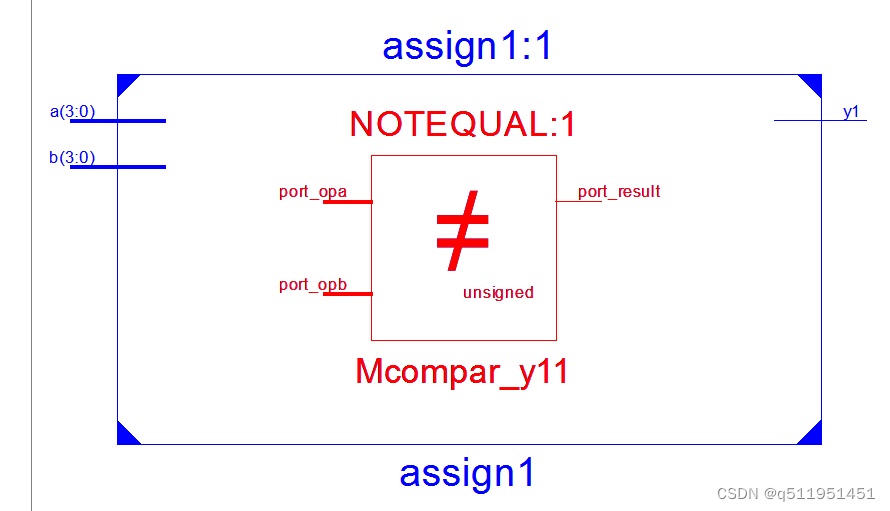

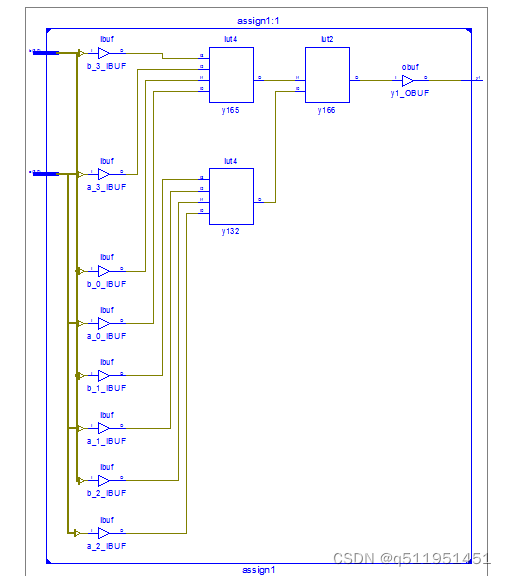

RTL结构图

技术原理图

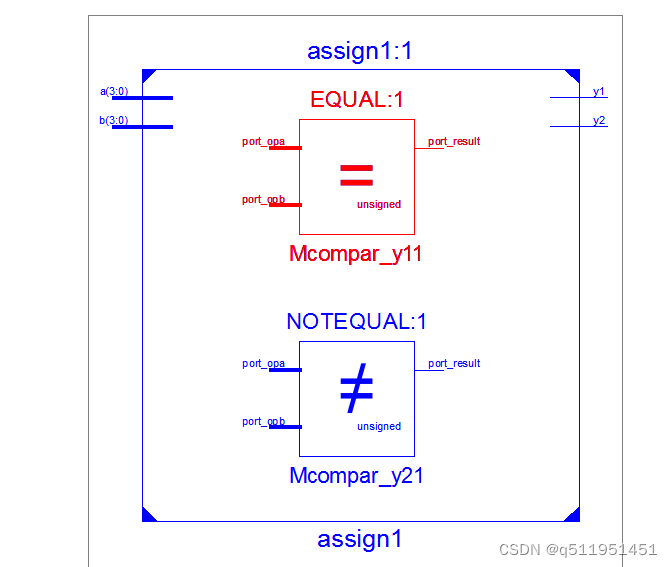

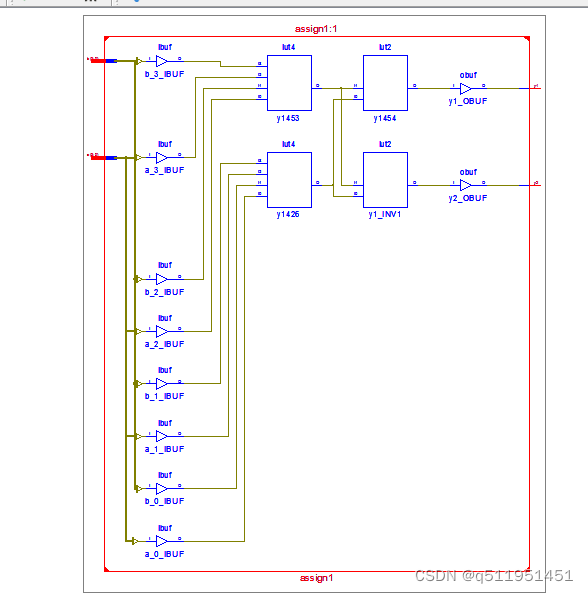

8. 等于与不等于比较器

代码

module assign1(

input[3:0] a,b,

output y1,

output y2

);

assign y1 = a==b; // 取出某一位

assign y2 = a!=b; // 取出某一位

endmodule

RTL结构图

技术原理图

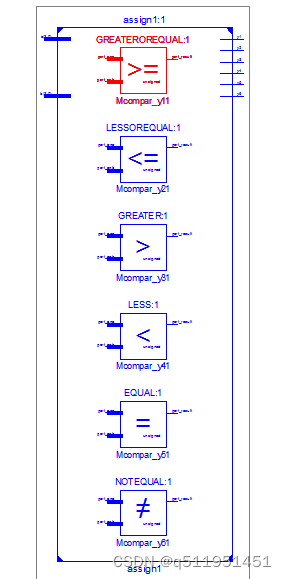

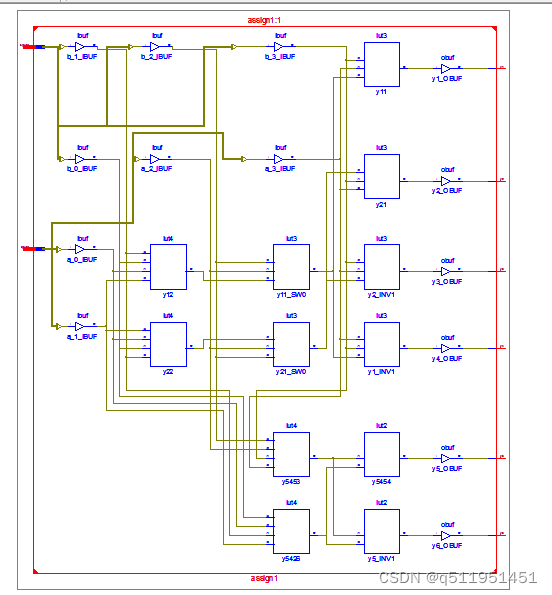

9 所有比较器综合比较

代码

module assign1(

input[3:0] a,b,

output y1,

output y3,

output y4,

output y5,

output y6,

output y2

);

assign y1 = a>=b;

assign y2 = a<=b;

assign y3 = a>b;

assign y4 = a<b;

assign y5 = a==b;

assign y6 = a!=b;

endmodule

RTL结构图

技术原理图

10 .? 逻辑非 !

代码

module assign1(

input[3:0] a,b,

output y1,

output y2

);

assign y1 = !a; // 取出某一位

endmodule

RTL结构图,结构图来看,逻辑非是判断输入的各个位都为0时,输出1,否则输出0,因此采用了一个与门逻辑,并且对输入的各个位取反。

技术原理图

11. 逻辑或 &&

module assign1(

input[3:0] a,b,

output y1,

output y2

);

assign y1 = a&&b; // 取出某一位

endmodule

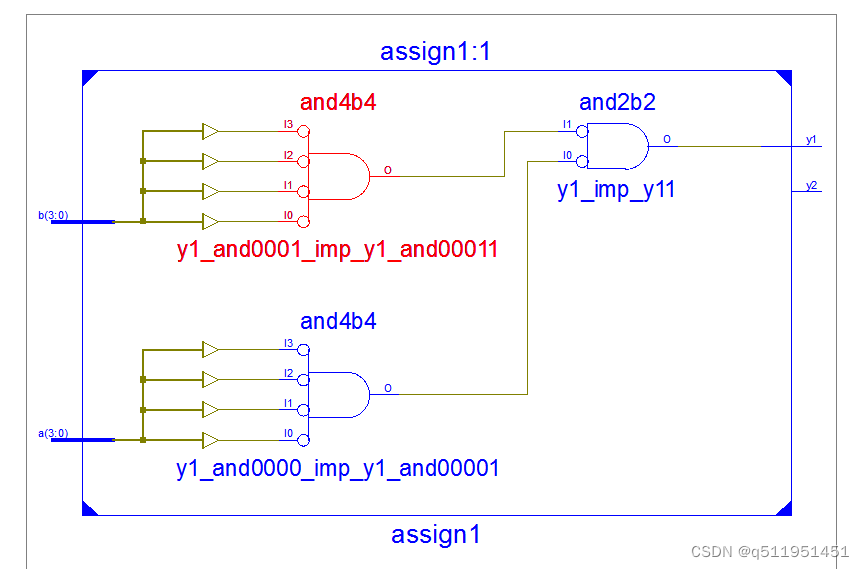

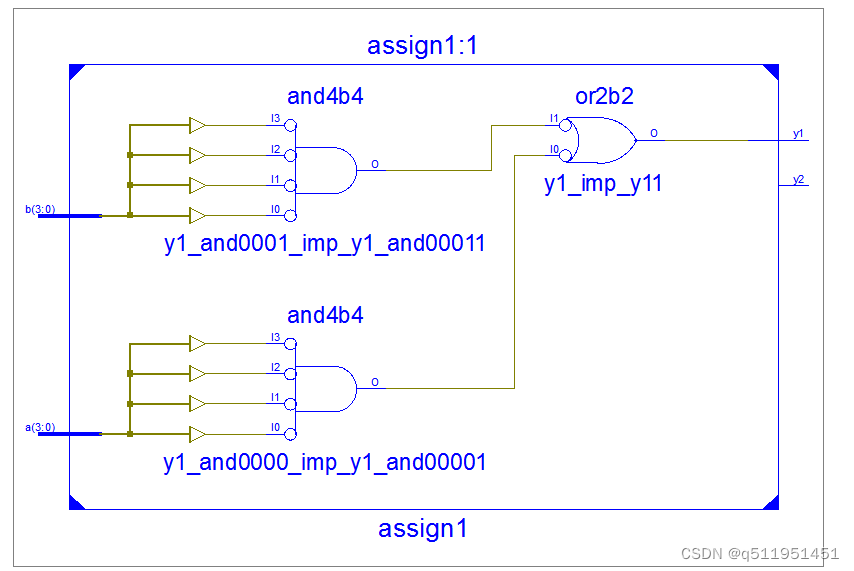

RTL结构图,从结构图来看,分别对两个输入进行逻辑非计算,然后对两个非输出再次进行逻辑非计算。

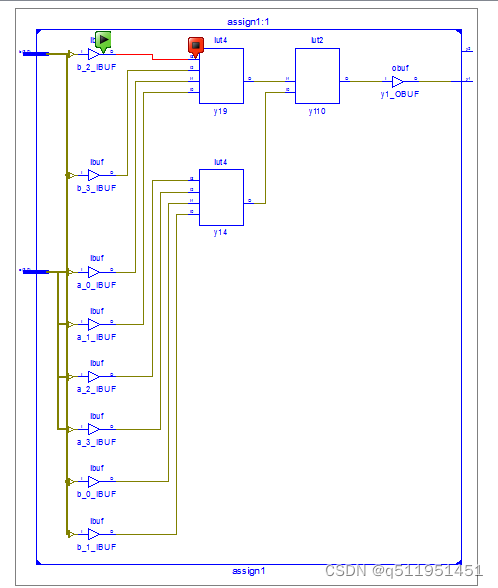

技术原理图

12. 逻辑或||

代码

module assign1(

input[3:0] a,b,

output y1,

output y2

);

assign y1 = a||b; // 取出某一位

endmodule

RTL结构图,逻辑或||运算首先对两个输入分别进行逻辑非运算,然后对输出的结果进行或非运算。

技术原理图

总结

逻辑比较器运算符电路都是组合逻辑电路,FPGA通过LUT查找表来实现。虽然逻辑运算符可以通过取反得到另外一种逻辑运算符,这样可以简化电路的结构,但是FPGA综合工具并没有这么处理,主要是为了减少电路的延时门长度,通过牺牲资源来梯形逻辑运算的响应速度。此外所有的逻辑运算符在FPGA中,都是通过从新组合成电路来实现的。FPGA相当于从新构造运算单元来完成计算的。这是FPGA与CPU的区别的主要特征。CPU的算术运算单元是固有的,使用的时候通过指令进行调用就行了。另外,LUT查找表再次扮演了组合逻辑设计的重要角色,原理上能够完成所有逻辑运算器电路的设计。当然对于高性能的设计,还需要借助进位链来实现。

通过逻辑运算单元的测试,进一步体验了一把基本逻辑运算的概念与电路之间的关系,对于理解计算机,FPGA等基本结构有很大的帮助,是性能优化以及设计芯片的基础。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!