【二段式状态机】 fsm 输出打一拍写法

2024-01-02 19:41:00

https://blog.csdn.net/ONEFPGA/article/details/125297745

fsm 2 process

module auto_sell(

input clk,

input rst_n,

input coin_one,

input coin_half,

output reg water,

output reg coin_back

);

parameter ZERO = 3'b000;

parameter HALF = 3'b001;

parameter ONE = 3'b010;

parameter ONE_HALF = 3'b011;

parameter TWO = 3'b100;

//--------------------二段式 1 ok--------------------------

//二段式状态机

reg [2:0] c_status;

reg [2:0] n_status;

reg water_reg; //new 新加的部分;

reg coin_back_reg; //new

//状态转移

always@(posedge clk,negedge rst_n)begin

water_reg <= water; //new

coin_back_reg <= coin_back; //new

if(!rst_n)

c_status <= ZERO;

else

c_status <= n_status;

end

//描述状态转移规律以及输出

always@(posedge clk,negedge rst_n)begin

if(!rst_n)

begin

n_status <= ZERO;

water <= 1'b0;

coin_back <= 1'b0;

end

else

case(c_status)

ZERO :

begin

water <= 1'b0;

coin_back <= 1'b0;

if(coin_half)

n_status <= HALF;

else if(coin_one)

n_status <= ONE;

else

n_status <= ZERO;

end

HALF :

begin

water <= 1'b0;

coin_back <= 1'b0;

if(coin_half)

n_status <= ONE;

else if(coin_one)

n_status <= ONE_HALF;

else

n_status <= HALF;

end

ONE :

begin

water <= 1'b0;

coin_back <= 1'b0;

if(coin_half)

n_status <= ONE_HALF;

else if(coin_one)

n_status <= TWO;

else

n_status <= ONE;

end

ONE_HALF :

begin

water <= 1'b0;

coin_back <= 1'b0;

if(coin_half)

n_status <= TWO;

else if(coin_one)

begin

n_status <= ZERO;

water <= 1'b1;

coin_back <= 1'b0;

end

else

n_status <= ONE_HALF;

end

TWO :

begin

water <= 1'b0;

coin_back <= 1'b0;

if(coin_half)

begin

n_status <= ZERO;

water <= 1'b1;

coin_back <= 1'b0;

end

else if(coin_one)

begin

n_status <= ZERO;

water <= 1'b1;

coin_back <= 1'b1;

end

else

n_status <= TWO;

end

default:

n_status <= ZERO;

endcase

end

endmodule

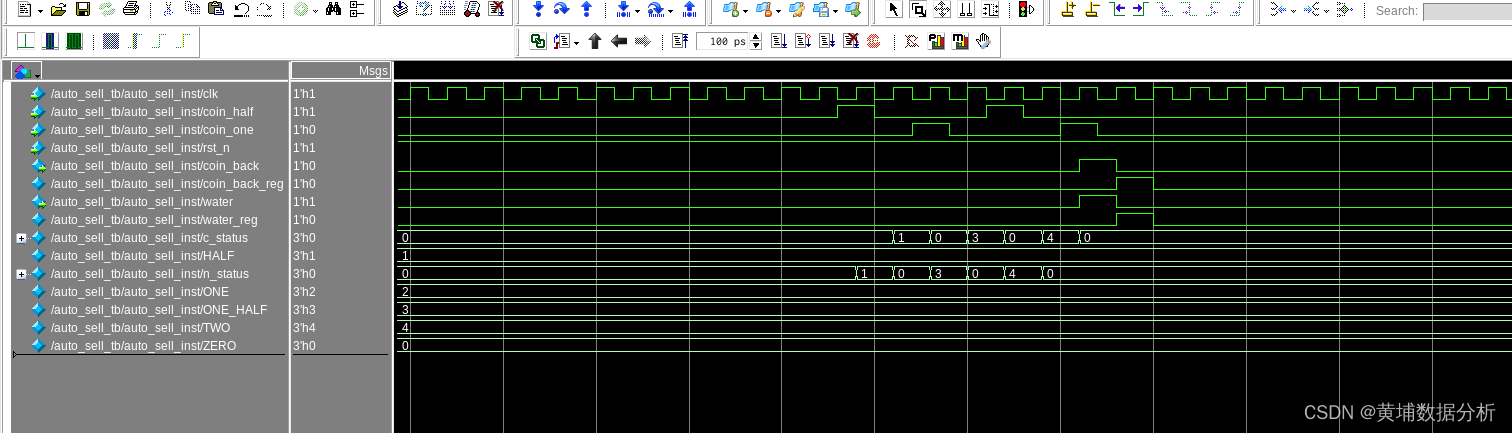

testbench

`timescale 1ns/1ps

module auto_sell_tb;

reg clk;

reg rst_n;

reg coin_one;

reg coin_half;

wire water;

wire coin_back;

initial begin

clk = 0;

rst_n = 0;

coin_one = 0;

coin_half = 0;

#20;

rst_n = 1;

//延时200us

#10000

//投2.5元

coin_half = 1;

#20;

coin_half = 0;

#20;

coin_one = 1;

#20;

coin_one = 0;

#20;

coin_half = 1;

#20;

coin_half = 0;

#20;

coin_half = 1;

#20;

coin_half = 0;

#20;

//延时200us

#10000

//投3元

coin_half = 1;

#20;

coin_half = 0;

#20;

coin_one = 1;

#20;

coin_one = 0;

#20;

coin_half = 1;

#20;

coin_half = 0;

#20;

coin_one = 1;

#20;

coin_one = 0;

#20;

//延时200us

#10000

$stop;

end

auto_sell auto_sell_inst(

.clk (clk),

.rst_n (rst_n),

.coin_one (coin_one),

.coin_half (coin_half),

.water (water),

.coin_back (coin_back)

);

always #10 clk = ~clk;

endmodule

文章来源:https://blog.csdn.net/weixin_39060517/article/details/135345383

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!