【FPGA/verilog -入门学习7】 条件判断if与分支判断case语句的语法介绍

2023-12-13 17:32:21

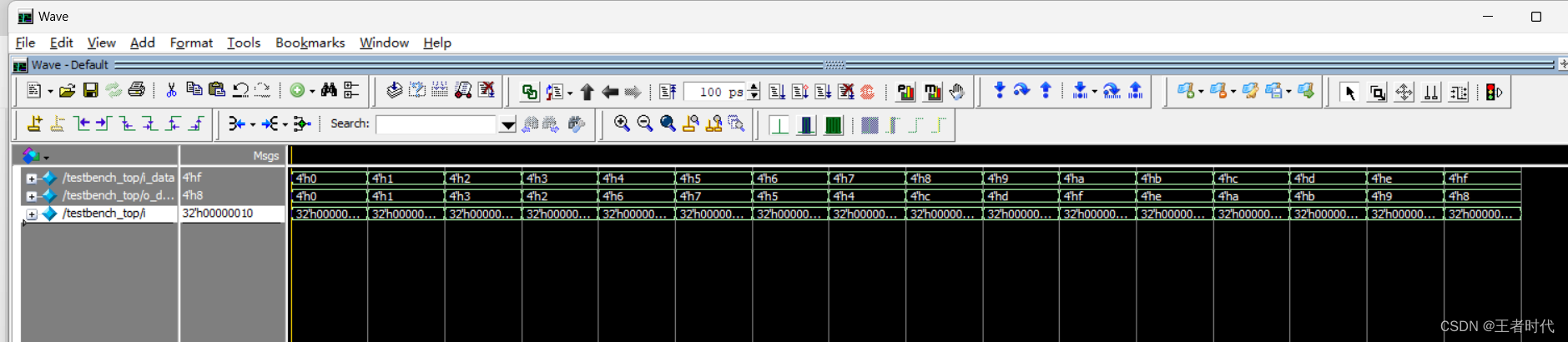

需求 使用if 和case ?产生格雷码

/

/*

条件判断if与分支判断case语句的语法介绍

需求 使用if 和case 产生格雷码

*/

/

`timescale 1ns/1ps

module vlg_design(

input [3:0] i_data,

output reg [3:0] o_data,

output reg [3:0] o_datac

);

always @(*) begin

if (4'b0000 == i_data) o_data <= 4'b0000;

else if(4'b0001 == i_data) o_data <= 4'b0001;

else if(4'b0010 == i_data) o_data <= 4'b0011;

else if(4'b0011 == i_data) o_data <= 4'b0010;

else if(4'b0100 == i_data) o_data <= 4'b0110;

else if(4'b0101 == i_data) o_data <= 4'b0111;

else if(4'b0110 == i_data) o_data <= 4'b0101;

else if(4'b0111 == i_data) o_data <= 4'b0100;

else if(4'b1000 == i_data) o_data <= 4'b1100;

else if(4'b1001 == i_data) o_data <= 4'b1101;

else if(4'b1010 == i_data) o_data <= 4'b1111;

else if(4'b1011 == i_data) o_data <= 4'b1110;

else if(4'b1100 == i_data) o_data <= 4'b1010;

else if(4'b1101 == i_data) o_data <= 4'b1011;

else if(4'b1110 == i_data) o_data <= 4'b1001;

else if(4'b1111 == i_data) o_data <= 4'b1000;

else o_data <= 4'b0000;

end

always @(*) begin

case (i_data)

4'b0000 :o_datac <= 4'b0000;

4'b0001 :o_datac <= 4'b0001;

4'b0010 :o_datac <= 4'b0011;

4'b0011 :o_datac <= 4'b0010;

4'b0100 :o_datac <= 4'b0110;

4'b0101 :o_datac <= 4'b0111;

4'b0110 :o_datac <= 4'b0101;

4'b0111 :o_datac <= 4'b0100;

4'b1000 :o_datac <= 4'b1100;

4'b1001 :o_datac <= 4'b1101;

4'b1010 :o_datac <= 4'b1111;

4'b1011 :o_datac <= 4'b1110;

4'b1100 :o_datac <= 4'b1010;

4'b1101 :o_datac <= 4'b1011;

4'b1110 :o_datac <= 4'b1001;

4'b1111 :o_datac <= 4'b1000;

default: o_datac <= 4'b0000;

endcase

end

endmodule

`timescale 1ns/1ps

module testbench_top();

//参数定义

//接口申明

reg [3:0]i_data;

wire[3:0]o_data;

wire[3:0]o_datac;

vlg_design uut_vlg_design(

.i_data(i_data),

.o_data(o_data)

.o_datac(o_datac)

);

integer i;

//时钟和复位初始化、复位产生

initial begin

for(i = 0;i<16;i = i+1) begin

i_data <= i;

#10;

end

end

endmodule

文章来源:https://blog.csdn.net/cengqiu4314/article/details/134915928

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!