W5100S-EVB-Pico评估版介绍

2023-12-25 15:34:15

1 简介

??W5100S-EVB-Pico是一款基于树莓派RP2040和全硬件TCP/IP协议栈以太网芯片W5100S的MCU评估板,其工作原理与树莓派Pico板基本相同,但通过W5100S增加了以太网。

2 硬件资源

2.1 硬件规格

- RP2040 微控制器,配备2MByte Flash

- 双核 Arm Cortex-M0 + @ 133MHz

- 芯片内置 264KB SRAM 和 2MB 的板载闪存

- 通过专用 QSPI 总线支持最高 16MB 的片外闪存

- 30 个 GPIO 引脚,其中 4 个可用作模拟输入

- 1.8-3.3V IO 电压 (注意:Pico IO电压固定为3.3V)

- 12位500ksps模拟数字转换器(ADC)

- 丰富的外设

- 2 × UART, 2 × I2C, 2 × SPI, 16 × PWM 通道

- 1 × Timer 和 4 x alarms, 1 × RTC

- 8个树莓派可编程 I/O(PIO)状态机,用于自定义外围设备支持

- 灵活且可编程的高速IO

- 支持模拟SD卡和VGA等接口

- W5100S

- 全硬件TCP/IP协议栈

- 支持丰富的协议: TCP, UDP, UDP协议上的WOL, ICMP, IGMPv1/v2, IPv4, ARP, PPPoE

- 硬件协议栈不受网络攻击,安全稳定

- 4个独立的硬件socket,各路通信互不影响

- 16KB片上缓存供TCP/IP包处理

- 高速SPI接口

- 全硬件TCP/IP协议栈

- Micro-USB接口,用于供电和传输数据(通过拖放烧录程序)

- 3针ARM串行线调试(SWD)端口

- 内置10 / 100 以太网 PHY

- 全/半双工,10/100速率自动协商

- 内置RJ45(RB1-125BAG1A)

- 内置LDO (LM8805SF5-33V)

2.2 引脚定义

??如上图所示,W5100S-EVB-Pico引脚直接连接到RP2040的GPIO。它具有与树莓派Pico板相同的引脚。但是,GPIO16、GPIO17、GPIO18、GPIO19、GPIO20、GPIO21连接在板内的W5100S上。这些引脚使SPI通信与W5100S使用以太网功能。如果您正在使用以太网功能,这些引脚不能用于任何其他目的。

??W5100S-EVB-Pico内部使用的RP2040 GPIO如下表所示:

| I/O | 引脚名 | 描述 |

|---|---|---|

| I | GPIO16 | 连接至W5100S的MISO接口 |

| O | GPIO17 | 连接至W5100S的CS接口 |

| O | GPIO18 | 连接至W5100S的SCLK接口 |

| O | GPIO19 | 连接至W5100S的MOSI接口 |

| O | GPIO20 | 连接至W5100S的RSTn接口 |

| I | GPIO21 | 连接至W5100S的INTn接口 |

| I | GPIO24 | VBUS检测接口 |

| O | GPIO25 | 连接至用户LED |

| I | GPIO29 | 用于ADC模式检测VSYS/3 |

?? 除了GPIO和接地引脚外,还有7个其他引脚接口:

| 引脚号 | 引脚名 | 描述 |

|---|---|---|

| PIN40 | VBUS | Micro-USB输入电压,连接至Micro-USB接口引脚1。理论上支持5V。 |

| PIN39 | VSYS | 主系统输入电压,可在4.3V到5.5V额允许范围内变化,由板载LDO产生3.3V |

| PIN37 | 3V3_EN | 连接到板载LDO使能引脚。要禁用3.3V(也使RP2040和W5100S断电),将此引脚拉低。 |

| PIN36 | 3V3 | 主3.3V电源,用来给RP2040和W5100S供电,由板载LDO产生。 |

| PIN35 | ADC_VERF | ADC电源(和参考)电压,并在W5100S-EVB-Pico上通过滤波3.3V电源产生。 |

| PIN33 | AGND | GPIO26-GPIO29接地参考。 |

| PIN30 | RUN | RP2040使能引脚。复位RP2040则将该引脚拉低。 |

2.3 工作条件

| 属性 | 参数 |

|---|---|

| 工作温度 | -20℃~85℃ |

| Micro-USB输入电压 | DC 5V(+/- 10%) |

| 输入电压 | DC 4.3V~5.5V |

3 参考资料

3.1 Datasheet

RP2040 Datasheet:https://datasheets.raspberrypi.org/rp2040/rp2040-datasheet.pdf

W5100S Datasheet:https://docs.wiznet.io/Product/iEthernet/W5100S/overview

3.2 原理图

W5100S:https://github.com/Wiznet/Hardware-Files-of-WIZnet/tree/master/02_iEthernet/W5100S/W5100S-EVB-Pico

3.3 尺寸图(单位:mm)

3.4 参考例程

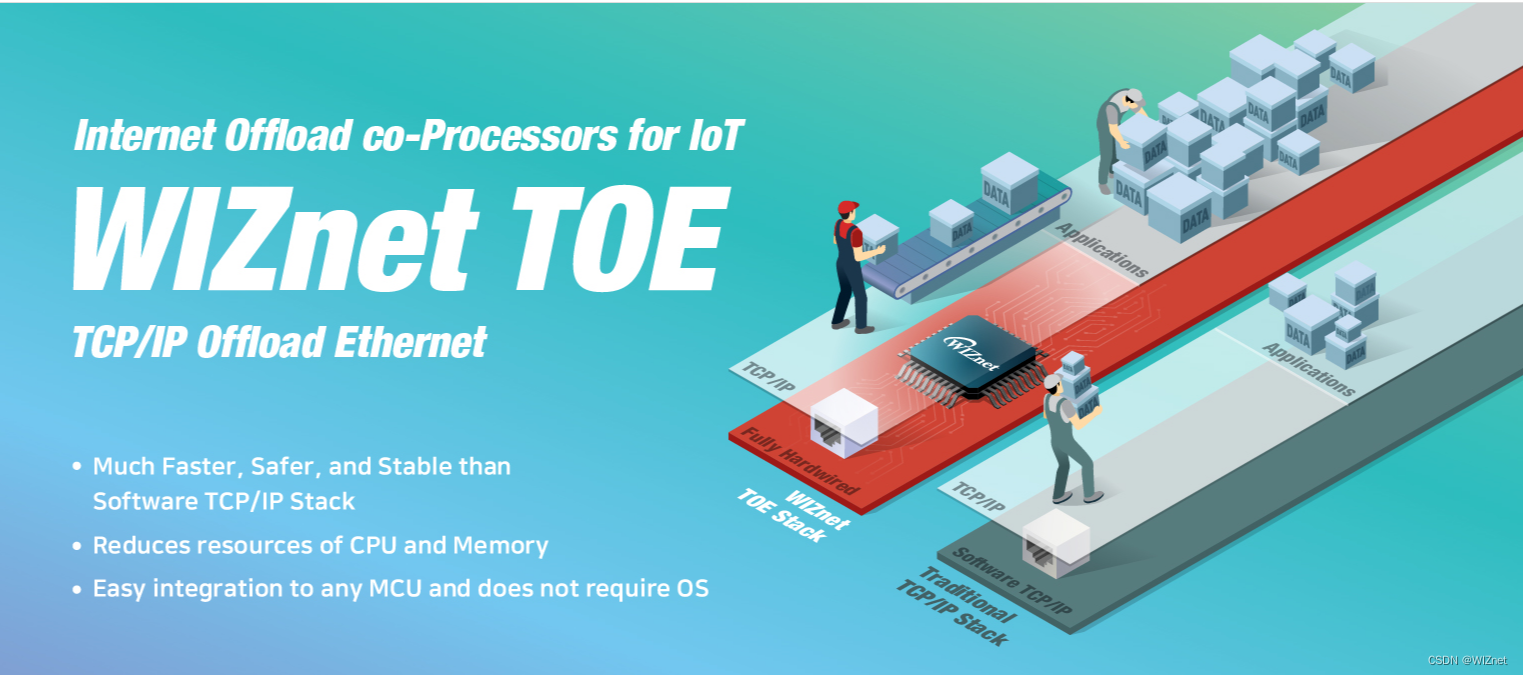

4 硬件协议栈优势

- 高效性:硬件协议栈将TCP/IP协议中的传输层和网络层集成到了一颗以太网芯片中,实现了真正的TCP/IP卸载引擎技术(ToE),为单片机减负,缩短了开发周期。

- 稳定性:硬件协议栈在高速通信时依然保持稳定,其传输速率是单纯软件协议栈的两倍之多。

- 安全性:由于TCP/IP在主系统外独立运行,因此能有效地防止外部恶意网络攻击。

- 易用性:硬件协议栈易于使用,开发者无需专业的网络知识,如同控制外部存储器一样简单,真正实现网络的透明传输。

- 高吞吐率:硬件协议栈有效地卸载主芯片TCP/IP处理负载,释放更多的CPU资源。

文章来源:https://blog.csdn.net/WIZnet2012/article/details/135198702

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!