【上海大学数字逻辑实验报告】六、时序电路

一、 实验目的

- 掌握同步二进制计数器和移位寄存器的原理。

- 学会用分立元件构成2位同步二进制加计数器。

- 学会在Quartus II上设计单向移位寄存器。

- 学会在Quartus II上设计环形计数器。

二、 实验原理

-

同步计数器是指计数器中的各触发器的时钟脉冲输入端连接在一起,接到输入的计数脉冲的CP端,所以各触发器在同一时钟脉冲的作用下,其翻转是同步进行的。

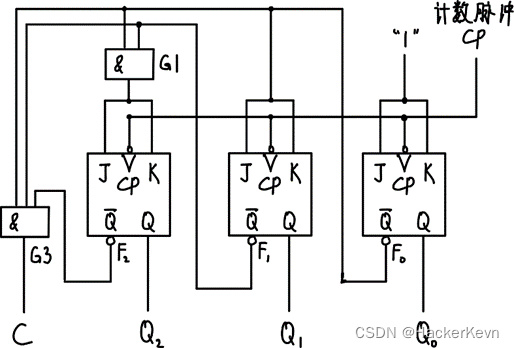

下面是一个用JK触发器构造的4位同步二进制加计数器:

由图可知:

所以电路的输出方程即进位为:

注意:

①. 上述方程均在CP下降沿有效。

②. 计数前应清零,清零后每当输入一个脉冲,计数器将按加1规律变化。

- 74LS74是一种双D触发器芯片,它具有12个引脚,其中8个输入引脚,4个输出引脚,其逻辑电路图如下图所示:

74LS74的引脚中:

输入端:1D、2D

时钟输入端:1CLK、2CLK

直接置位端(低电平有效):1PRN、2PRN

直接复位端(低电平有效):1CLRN、2CLRN

输出端:1Q、1QN、2Q、2QN

三、实验内容

实验任务一:用74LS112芯片构成2位同步二进制加计数器

(1) 实验步骤

- 将74LS112的输入引脚1J和1K同时连接到K16,输入引脚2J、2K同时连接到输出引脚1Q,输入引脚1CLK连接到连续脉冲1H,输入引脚1PRE、1CLR、2PRE、2CLR分别连接K5、K6、K8、K7,最后将输出引脚1Q和2Q分别连接到数码管LED6和LED5,接电接地后所构成的2位同步二进制加计数器如下所示:

- 将2位同步二进制加计数器清零,拨动开关,观察数码管的变化。

(2) 实验现象

①. 计数器清零时,数码管的值为0。

②. 当时钟脉冲到达时,计数器的值递增。

③. 当计数器的值达到最大也就是3时,它将从0重新开始计数。

(3) 实验结论

通过74LS112作为搭建平台,我们成功地实现了一个2位同步二进制加计数器。实验结果表明,计数器能按照预期进行计数。

实验任务二:在Quartus II用2片双D触发器74LS74构成单向移位寄存器

(1) 实验步骤

- 用Quartus II设计出如下电路:

- 编译通过后进行波形仿真,验证电路逻辑功能:

- 仿真通过后,参照原理图定义引脚:

- 生成编程并将文件下载到FPGA。

- 将开关连接对应的输入引脚,输出引脚连接到发光二极管:

- 用开关和发光二极管测试FPGA的功能。

- 记录测试结果。

(2) 实验现象

①. 在开始时,环形计数器为初始值。

②. 当时钟脉冲到达时,数据会按照时钟脉冲的触发进行移位,也就是数据从第一个74LS74移位到第二个74LS74,第一个74LS74的Q输出变为新的数据,第二个74LS74的Q输出也变为新的数据。

(3) 实验结论

通过使用Quartus II设计工具,我们成功地用74LS74设计了一个单向移位寄存器。实验结果表明,数据会按照时钟脉冲的触发进行移位,符合预期行为。

实验任务三:在Quartus II上设计环形计数器

(1) 实验步骤

- 用Quartus II设计出如下电路:

- 编译通过后进行波形仿真,验证电路逻辑功能:

- 仿真通过后,参照原理图定义引脚:

- 生成编程并将文件下载到FPGA。

- 将开关连接对应的输入引脚,输出引脚连接到发光二极管:

- 用开关和发光二极管测试FPGA的功能。

- 记录测试结果。

(2) 实验现象

①. 在开始时,环形计数器为初始值。

②. 当时钟脉冲到达时,数据会按照时钟脉冲的触发进行移位,也就是数据从第一个74LS74移位到第二个74LS74,第一个74LS74的Q输出变为新的数据,第二个74LS74的Q输出也变为新的数据。

③. 当移动到最高位后,环形计数器将返回到初始值,形成一个循环。

(3) 实验结论

通过使用Quartus II设计工具,我们成功地用74LS74设计了一个环形计数器。实验结果表明,数据会按照时钟脉冲的触发进行移位并循环,符合预期行为。

四、思考题

(1) 如何构成3位同步二进制加(减)计数器?

3位同步二进制加计数器电路图:

3位同步二进制减计数器电路图:

(2) 如何用74LS74构成双向移位寄存器?

答:在构成单向移位寄存器的基础上,只需要改变左移、右移的控制信号即可以实现双向移位。

五、建议和体会

- 在实验前,要熟悉同步二进制计数器和移位寄存器的原理。

- 实现环形计数器时,必须设置适当的初态,这样电路才能实现计数。

- 本实验有助于增进对同步二进制计数器和移位寄存器的理解,同时也提供了一个实际的设计和模拟测试经验。为后续进行更复杂的电路设计打下基础。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!