verilog高级语法-原语-ibuf-obuf-LUT

2023-12-15 18:12:52

概述:

原语直接操作FPGA的资源,对FPGA的结构更加清晰,使用原语之前需要对FPGA的资源进行了解,本节为初识原语

学习内容

1. 输入缓冲原语 IBUF

2. 输出缓冲原语 OBUF

3. 查找表原语? ? LUT

1. IBUF,OBUF原语简介

输入输出端口必须添加缓冲后才能进入FPGA内部逻辑,用于与外部隔离。功能就是起到缓冲隔离的作用。

代码

IBUF b_IBUF (

.I(b),

.O(b_IBUF_3)

);

OBUF c_OBUF (

.I(c_OBUF_7),

.O(c)

);结构图

?

?

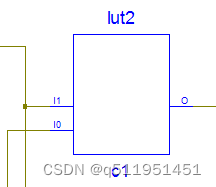

2. LUT查找表简介

代码 一个 c1=a|b逻辑功能的查找表代码如下

LUT2 #(

.INIT ( 4'hE ))

c11 (

.I0(a_IBUF_1),

.I1(b_IBUF_3),

.O(c1_OBUF_6)

);端口简介,LUT2也就是有2个输入地址线,分别对应组合逻辑的两个输入a,b。o为输出端口,也就的是得到的结果c1。具体功能就通过设计.INIT(4'hX)的值来决定,具体的功能看真值表的输出值,直接填上去。原理就是输入地址线的最小项的权重组成的数值。a|b的针织表如下图,也就是4'b1110≡4'hE。所以.INIT (4‘hE)就是这么来的

真值表

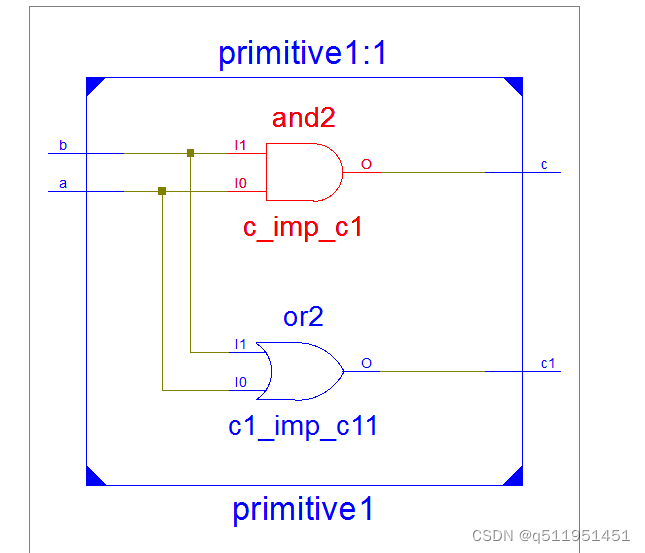

RTL结构图

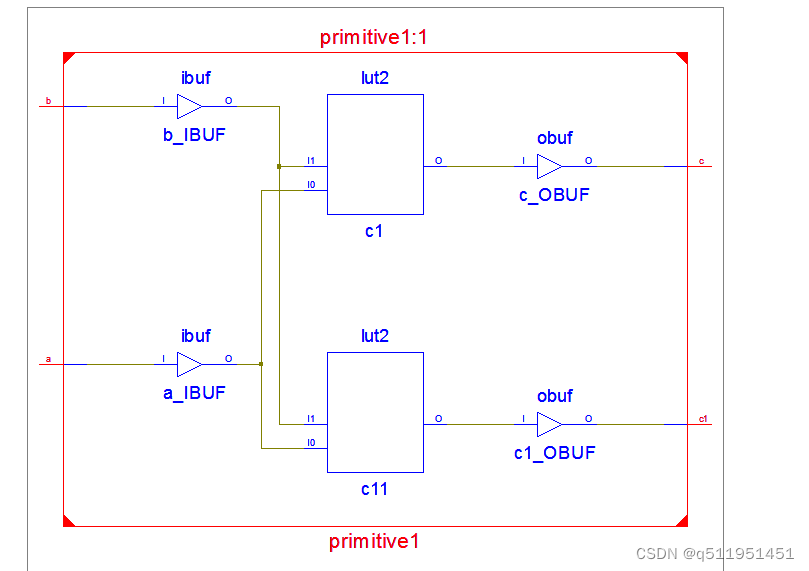

技术原理图

3. verilog c代码与原语代码比较

c代码

module primitive1(

input a,b,

output c,c1

);

assign c = a&b;

assign c1 = a|b;

endmodule原语代码

module primitive1 (

a, b, c, c1

);

input a;

input b;

output c;

output c1;

wire a_IBUF_1;

wire b_IBUF_3;

wire c1_OBUF_6;

wire c_OBUF_7;

LUT2 #(

.INIT ( 4'hE ))

c11 (

.I0(a_IBUF_1),

.I1(b_IBUF_3),

.O(c1_OBUF_6)

);

LUT2 #(

.INIT ( 4'h8 ))

c1_2 (

.I0(a_IBUF_1),

.I1(b_IBUF_3),

.O(c_OBUF_7)

);

IBUF a_IBUF (

.I(a),

.O(a_IBUF_1)

);

IBUF b_IBUF (

.I(b),

.O(b_IBUF_3)

);

OBUF c_OBUF (

.I(c_OBUF_7),

.O(c)

);

OBUF c1_OBUF (

.I(c1_OBUF_6),

.O(c1)

);

endmodule

RTL结构图

技术原理图

3. 总结

1. ibuf,obuf是端口缓冲,所有与外部相连接的端口都需要添加,用于电气隔离

2. FPGA使用LUT查找表实现组合逻辑,具体的功能可以通过设置.INIT中的值来实现,设置的值就是真值表的输出结果。

3. 原语是直接对FPGA电路结构进行操作和连接,设计开发效率比较低,但是他可以更好的利用底层资源进行设计,可以获得更加灵活的设计。

文章来源:https://blog.csdn.net/q511951451/article/details/135019928

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!