论文笔记_Generic_InP-Based_Integration_Technology:_Present_and_Prospects

Generic InP-Based Integration Technology: Present and Prospects

2014年

摘要:综述了当前基于InP的光子芯片代工厂的技术,并进行了展望

- 光子集成电路也有类似的摩尔定律,但是仍处在摩尔定律的早期

- 想要发展集成光学,需要借鉴集成电路发展过程中fabless与foundry模式及其一系列降低研发成本的方式

- 集成光芯片需要类似集成电路中三极管、二极管、电阻、电容、连接线等基本元件来制造通用集成光芯片

- 下一代集成光芯片是IMOS(InP membrane on silicon)

- 通过IMOS技术已经实现了大部分的光子基本器件,(涵盖了有源/无源器件),但仍有一些问题需要解决

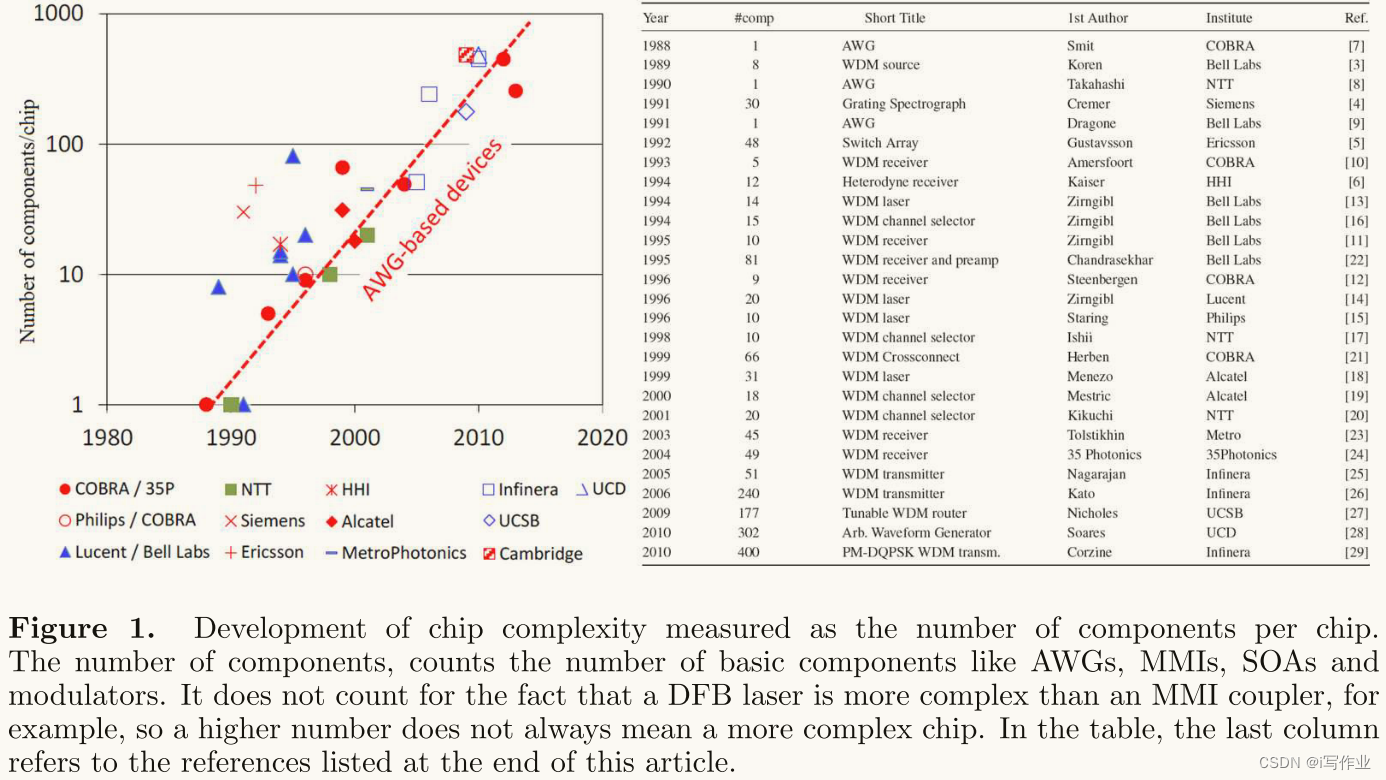

Ⅰ光子集成电路规模的发展

如图1所示,光芯片的发展也有类似于摩尔定律的趋势,不过现在在一个很早期的阶段(1988年1个芯片上1个光器件,2010年1个芯片上400个光器件)

1.1 集成光学与微电子学的区别

光学集成电路规模的发展和集成电路的发展很像,但是一些光学的固有特性使得集成电路成功的发展路径无法在集成光学中复现。以下是困难:

-

集成电路的生产线是高度专用化的,所以

-

一条生产线几乎就只会生产一种集成电路

-

一般的代工厂很难调整去生产光集成电路

-

全是小型生产线,不具备降低成本的潜力

-

最终会导致光子集成电路持续高价,进入不了市场

上述问题的解决办法分为两步:

- 开发一些支持实现大多数应用的通用光集成技术。(1.2节)

- 开发一些代工厂的基础设施来为代工厂提供可以低成本生产的通用技术。(1.3节)

-

1.2 通用集成光学的基本元件

对比电集成电路:

电子集成电路通过制造一些基本的单元(晶体管、二极管、电阻、电容、连接线等),并将这些单元通过不同的数量,以不同的拓扑结构连接来实现多种多样的集成电路。

光集成电路里可以做类似的事情:

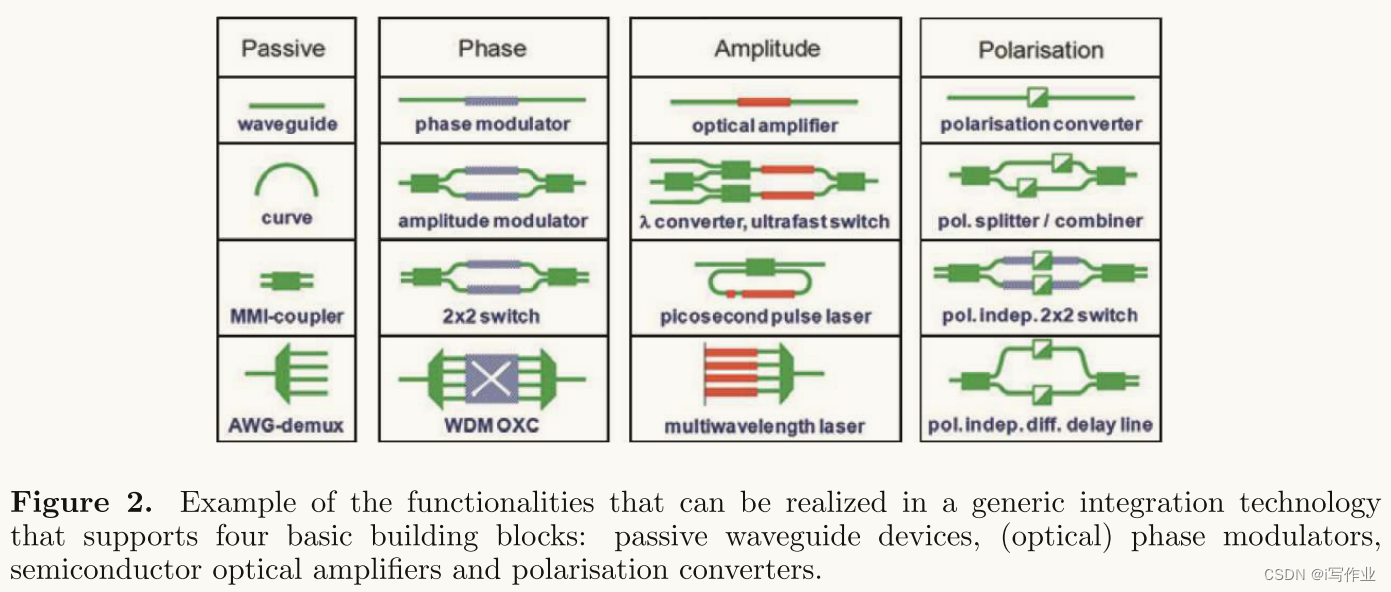

光集成电路也有一些基本元件:lasers, optical amplifiers, modulators, detectors and passive components like couplers, filters and (de)multiplexers. 不过作者给出了更为基本的4类元件,如图2所示。

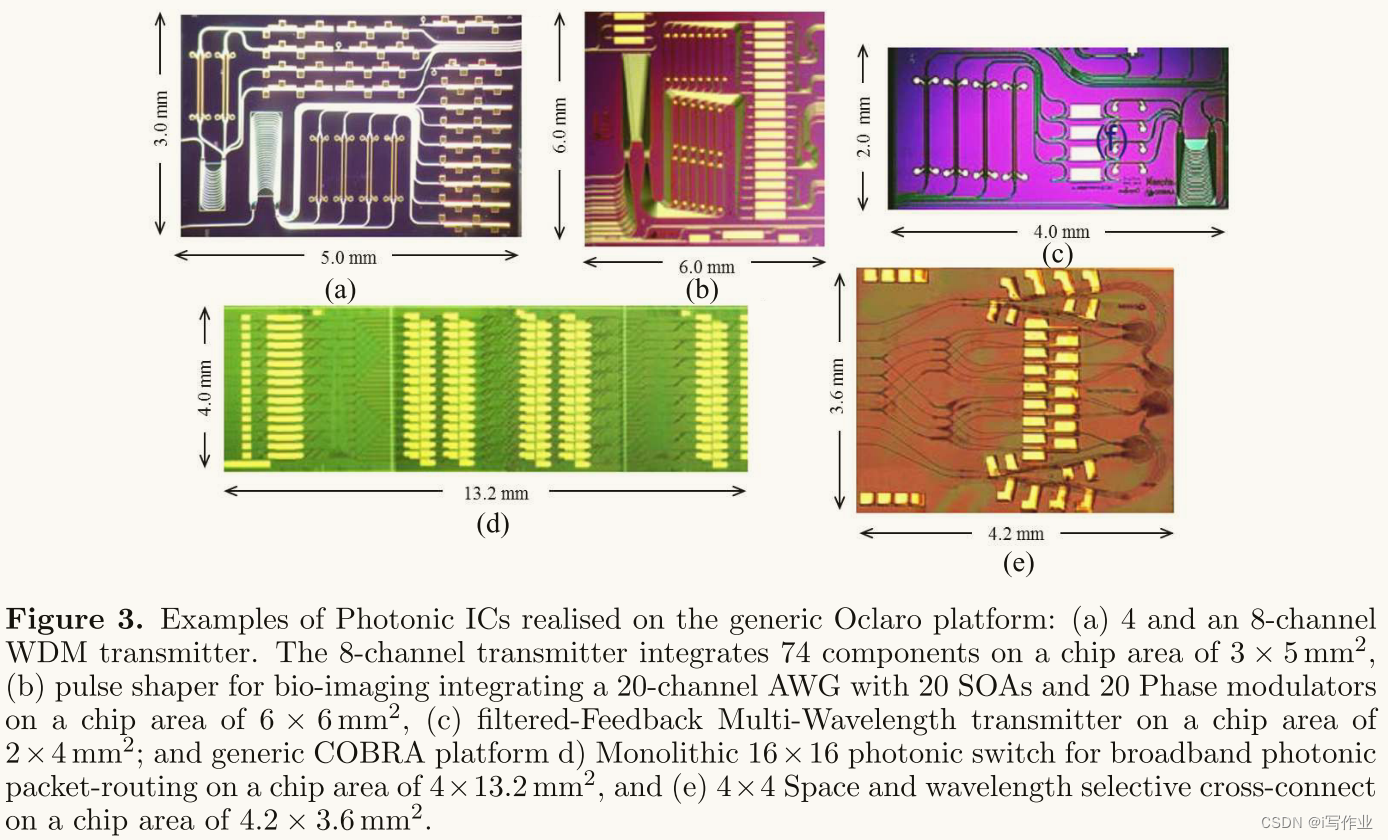

图3是一些用上述基本光学元件实现的光子集成电路

总的来说,这些基本器件的组合需要能够完成对光信号强度、相位、偏振的调制,才能支持光子集成芯片完成各种应用。(貌似没有提到频率调制呢)

通用集成技术的一个优点是,因为它们可以服务于一个大的市场,所以在开发基本元件(如图2)级别的高性能技术方面的投资是合理的。这将使其具有更强的竞争力。

1.3 Foundry模式以降低成本

对比电集成电路:

电集成电路采用Fabless与Foundry的公司模式,这样可以有效减少新入门的开销(因为不用建自己的fab,是跟其它芯片设计厂分摊生产线的开销)。

光子集成电路:

目前三个主要集成光学的制造平台:

- JePPIX——InP

- 功能性较强:包括集成激光器和功放

- ePIXfab——硅光

- 相比InP可以实现的功能,硅光做不了集成激光器和功放,但是因为与传统CMOS工艺兼容,所以成本更低、性能更好

-

TriPleX——主要做介质波导

-

在从可见光到红外的波长范围内,提供低损耗高质量的无源光学功能和一些有源热光功能

(offers low-loss and high quality passive optical functions and some thermo-optic active functions)

-

MPW(Multi-Project Wafer)可以有效的减少芯片制造的成本,而三上面这三个平台都支持MPW

这类代工厂需要能够完成以下6种工作:

- 通过全面或MPW运行,获得成熟和良好记录的商业铸造工艺

- 提供专用设计软件和组件库,以实现快速和准确的设计(设计套件)

- 中介服务:为不熟悉技术的用户提供帮助和培训

- 帮助没有设计自己芯片技术的公司设计芯片

- 提供可用的通用测试设施

- 提供可用的通用封装设备

1.4 通用集成光学的展望

- Foundry模式、MPW(Multi-Project Wafer)、芯片测试与封装过程中共享设备,可以有效的降低ASPIC研发的成本

- 希望可用通过提升基本光学元件(参考图2)的性能,来提高光子集成电路的性能(就像CMOS技术一样)

- 随着Foundry模式成熟带来成本的降低,光子集成电路可以在通信领域更具竞争力,获取更大的市场

- 随着PIC成本的降低,PIC也会渗透到其它领域

- 随着PIC成本的降低,PIC也会进入大公司,使其产品更具竞争力

- 对于无源器件,因为每个器件都会有损耗,所以在串联的数量上有限制

- 对于有源器件,通常都会有100mW左右的功率耗散,导致芯片发热,所以在功耗上会有限制

- 因为通过模拟信号传递信息的过程会存在噪声,所以在传递数字信息的过程中,每隔一段时间就需要一次信号重建,但是这需要额外的硬件资源

- 通用InP芯片的规模预计会止步在1000左右,如果需要更大规模的芯片,则需要其它的技术

Ⅱ 下一代光子集成电路:硅上InP掩膜(IMOS)

理论上,基于掩膜的集成光芯片可预见的优势有:

- 更大的规模

- 更低的功率耗散

目前存在的问题:

- 硅基光子集成电路存在的主要问题是光的产生和放大。硅基掩膜集成方案下,最具潜力的是Ⅲ-Ⅴ族的激光器(GaAs和InP可以制做较好的光源)

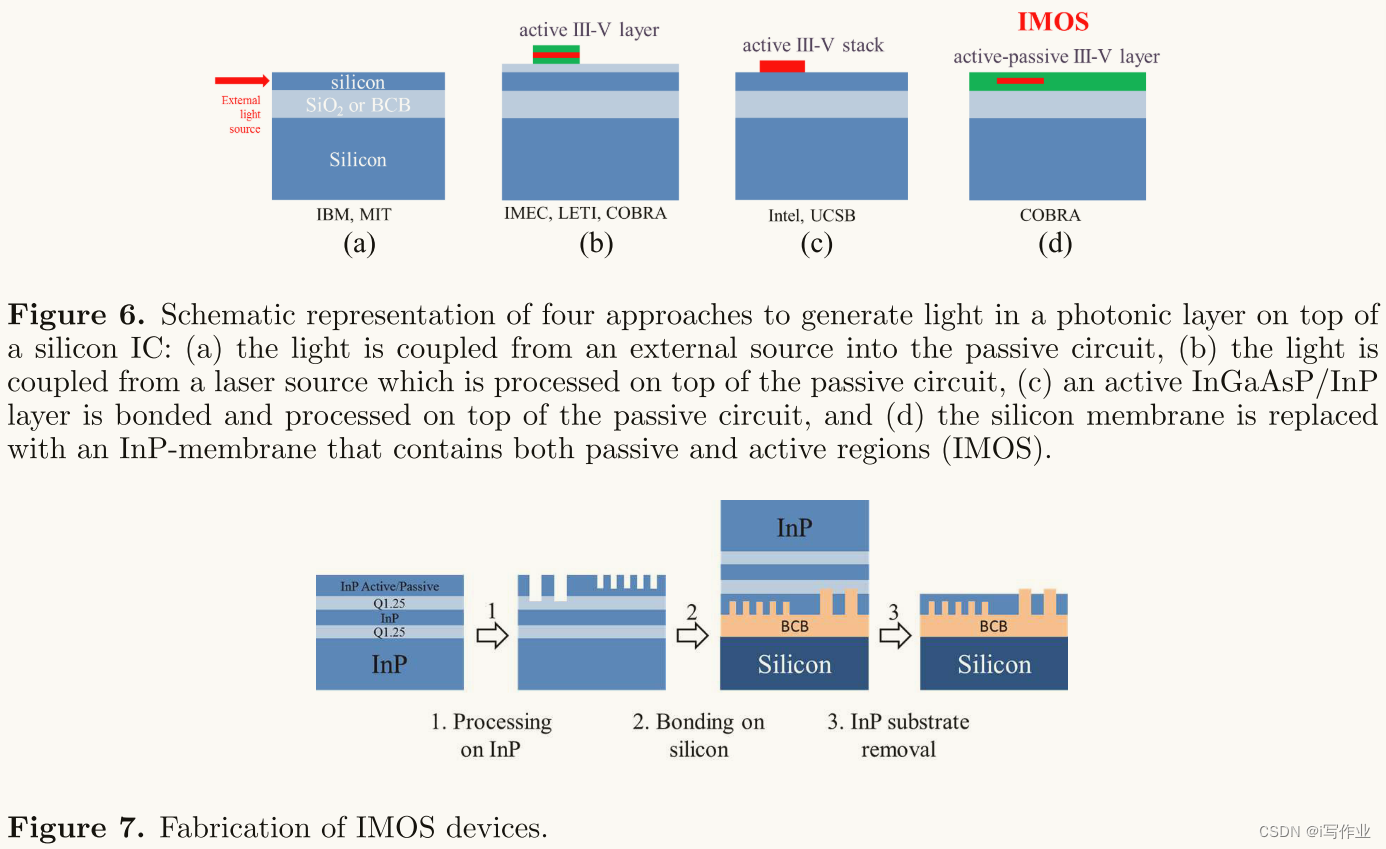

图6所示是4种硅光芯片的方案:

- (a) 方案的挑战性最小,但是缺少片上光源和放大器导致其规模上不去

- (b) 方案采用有源的Ⅲ-Ⅴ族激光器,建在硅片掩膜的上层。光通过下侧的薄、低折射率层进入到芯片中,但是光很难有效的耦合进硅层

- ? 方案,硅波导的增益是由直接在硅膜上的有源III-V族层的原子键合提供的,但是光从有源层到无源硅波导的耦合仍然困难,因为对高波导对光的约束和高耦合效率是矛盾的

- (d) 方案即作者推崇的方案(IMOS)

- 该方案可以直接集成有源器件(激光器、放大器),因此不存在前面光源难以耦合进波导的问题了

- 生产过程中对衬底对齐的需求也大大降低了

- 由于在衬底上使用了一层厚的聚合层来粘接InP掩膜,因此芯片性能几乎与表面形态无关

- 因为InP掩膜的过程与硅掩膜很像,所以有利于在未来实现光电混合芯片

图6结论:IMOS方案是未来

图7所示是IMOS(InP membrane on silicon)的制造过程,过程描述详见P8

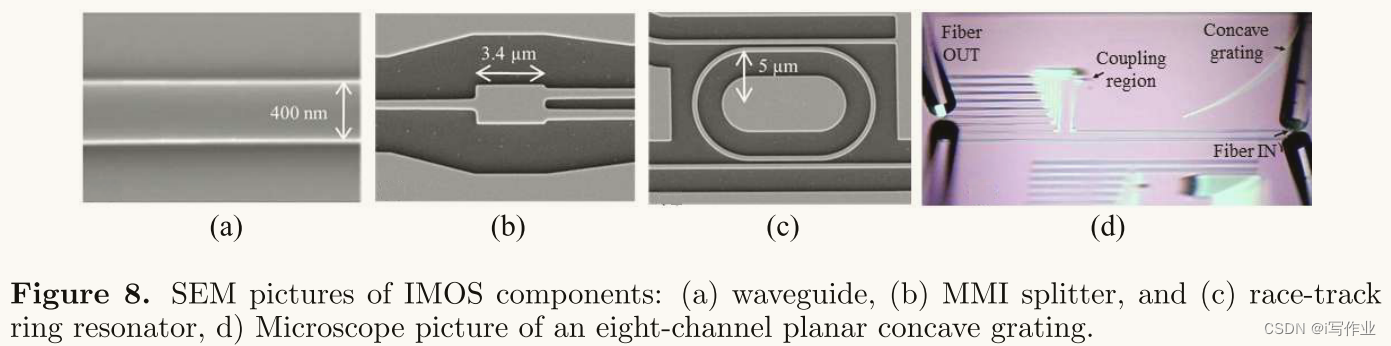

图8展示了一些已实现的基于IMOS技术的无源光器件:

- (a) 光波导,7dB/cm 的损耗

- (b) MMI分光器,0.6dB的损耗

- ? 跑道形谐振环,5μm的曲率,损耗几乎可以忽略不计

- (d) 8路平面凹形光栅(多路选择器),300nm厚的InP层,通道间串扰低于-18dB,插入损耗为2.8dB

- 环形滤波器,Q值(品质因数)超过15000(在参考文献[60])

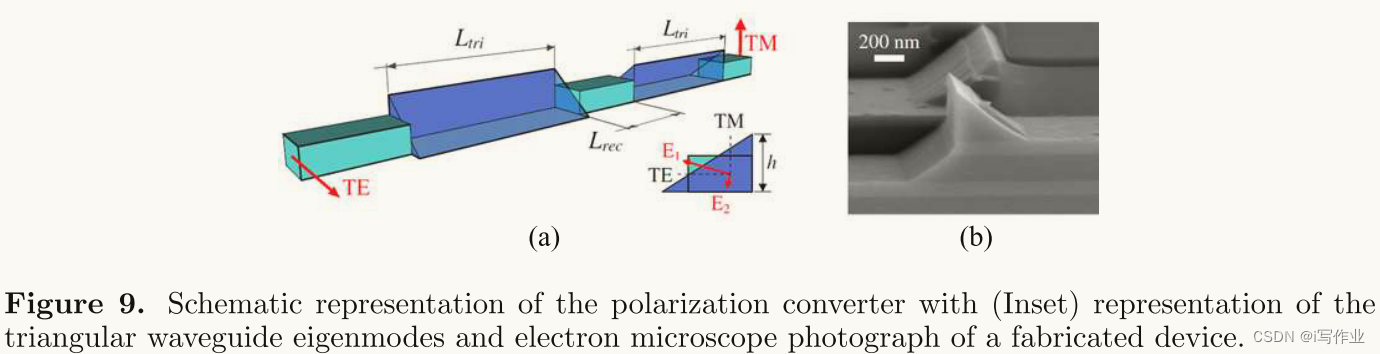

图9所示为其已实现的偏振调制器

- 长度 < 10μm

- 偏振调制效率 > 99%(在1.53μm的波长)

- 插入损耗 < 1.2dB(在1.53μm的波长)

- 此设计可以实现宽频带处理,并容忍一定的尺寸误差

IMOS方案已经实现了PIC光子集成电路所需的基本元件

有源与无源器件的集成需要注意2个问题:

- 有源/无源的界面应当光滑、平坦(不然会导致反射和散射)

- 加工过程中可能会破坏激发状态的量子阱材料

预计IMOS方案比传统的InP芯片的复杂度会高1个数量级

IMOS仍需解决的问题:

- 必须开发一种技术来有效地为薄膜上的有源器件提供电流和电压

- 需要解决膜的热管理和机械稳定性问题

IMOS仍有一些问题需要解决

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!