mipi dsi协议DBI/DPI接口

MIPI dsi协议中的DBI/DPI接口主要用于主机和display设备之间的数据传输,说的更通俗一点就是DSI RX控制器和实际的显示面板之间的接口;dsi 协议spec中对DBI/DPI有描述:

DSI协议中对DBI 接口模式命名为command mode operation,对DPI接口模式命名为video mode operation;

DBI接口:

DBI接口用于和display module本身具有显示控制和frame buffer之间,这有什么用呢?DBI接口最大的特点就是LCM自带framebuffer, 存储Host端发过来的数据, 并由内部的控制IC不断重复的刷到LCD上, 也就是说其内部实现了自刷新, Host只要发送一次数据即可, 这帧数据会一直显示在屏幕上。那没有显示控制和frame buffer的display module呢,我们下面会说。

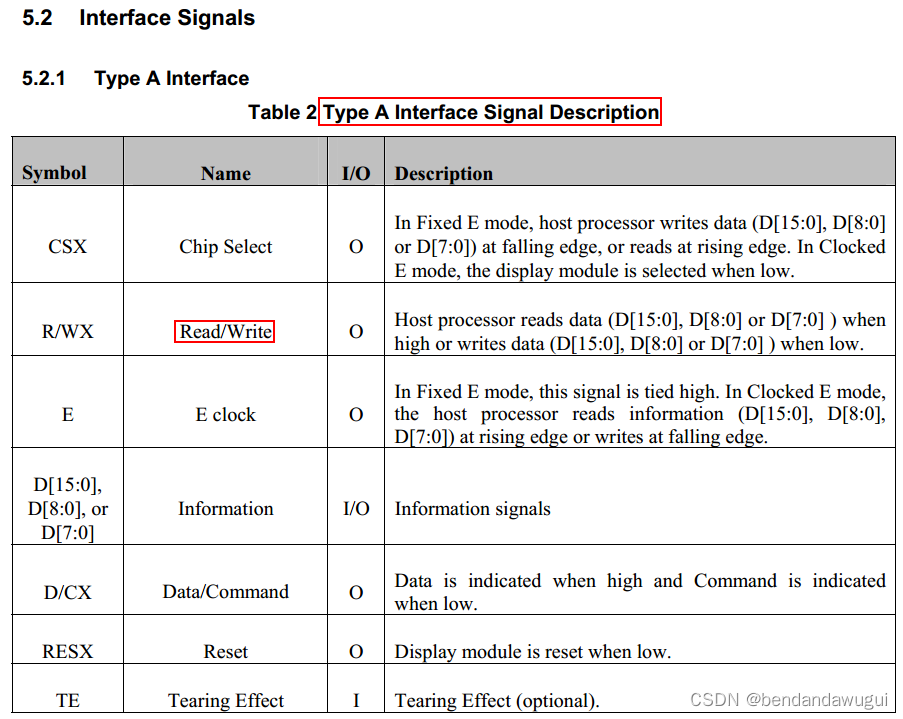

再来看看DBI接口的信号分别表示的意思:

除了typeA,协议还规定了typeB,typeC接口,具体的DBI type接口之间差异,大家感兴趣的可以查阅 MIPI Alliance Standard for Display Bus Interface spec;

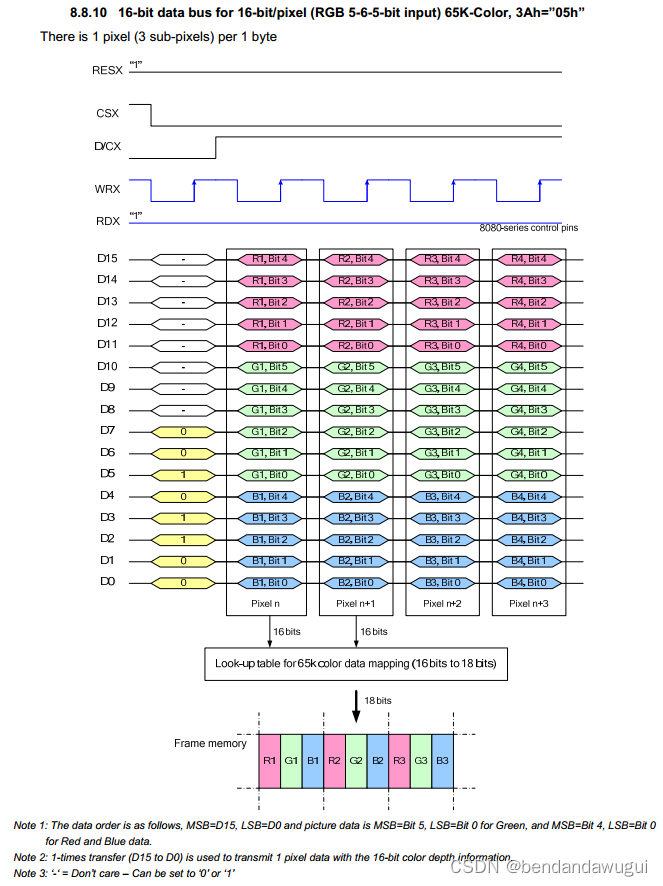

以RGB565为例,实际的数据传输如下图示,((2Ch): Memory Write, 写命令0x2c, 接着开始写帧数据?):

为啥要先通过DBI接口发出一个2ch的命令呢?通过查询dsi dcs spec可以得知,2ch是写mem start的指令,就是写display 的mem指令:

typeA的引脚中有一个比较重要的引脚TE引脚,它是一个host的输入引脚,display 屏幕可以通过这个引脚发出一帧数据是否刷完的信号;

上述截图是DBI spec中对TE引脚的时序描述,很明了的可以看出可以配置vsync或者vsync+hsync输出。

DSI 协议spec中对Tearing effect也有更为详细的描述:

specification for Display Serial Interface 2 (DSI-2SM) 8.12小节

DPI接口:

DPI接口,display pixel interface,也是用于主机和display设备之间的数据传输,与DBI不同的是,使用DPI接口的display 设备没有显示控制和frame buffer,主机为了维持画面能够持续的在屏幕上,要持续的发送数据过去,并且为保证数据的同步,引入vsync和hsync等功能;

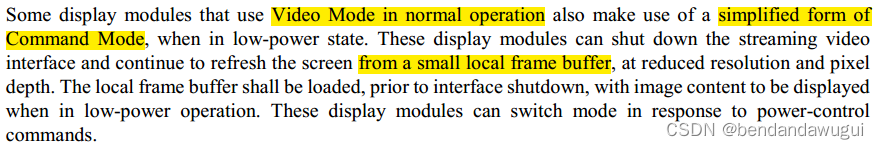

但是dsi spec中在DPI接口描述的小节也说到了一些使用DPI接口的显示设备为了能在低功耗时对屏幕进行刷新也有使用一个小的frame buffer来做屏幕刷新的操作。

接下来我们来看一下DPI接口的信号:

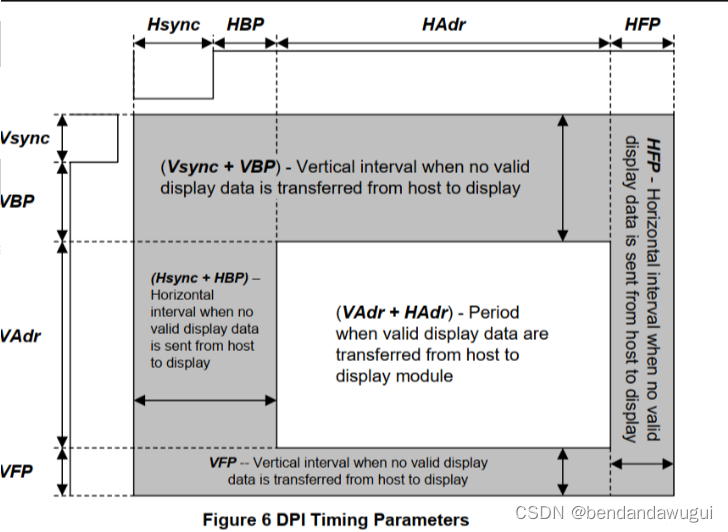

?看起来似乎很熟悉,没错DPI和VGA以及LCP都是一致的。那我们把DPI的时序贴上来:

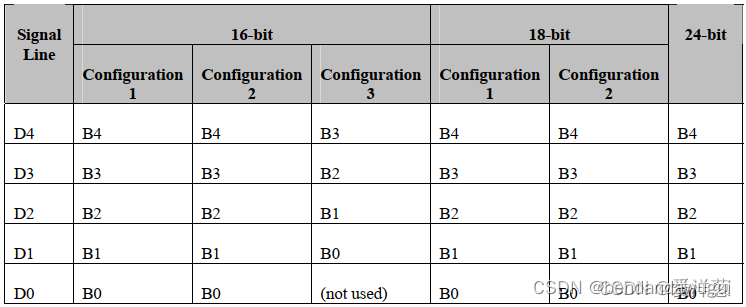

除了时序,还有一点需要注意的是,Color Coding,也就是当在使用 16 bit、18 bit、24 bit 来传输像素 RGB 数据的时候,几根线上的 RGB 通道是如何进行排列的:?

这里引出了 16bit 的 CFG1、CFG2、CFG3,以及 18bit 的 CFG1、CFG2;的配置;

参考文献:

MIPI Alliance Standard for Display Bus Interface

MIPI Alliance Standard for Display Pixel Interface

specification for Display Serial Interface 2 (DSI-2SM)

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!