ARM GIC(四) gicv3架构基础

GICv3架构是GICv2架构的升级版,增加了很多东西。变化在于以下:

使用属性层次(affinity hierarchies),来对core进行标识,使gic支持更多的core

将cpu interface独立出来,用户可以将其设计在core内部

增加redistributor组件,用来连接distributor和cpu interface

增加了LPI,使用ITS来解析

对于cpu interface的寄存器,增加系统寄存器访问方式

一、gicv3结构

包含了以下的组件:

distributor:SPI中断的管理,将中断发送给redistributor

redistributor:PPI,SGI,LPI中断的管理,将中断发送给cpu interface

cpu interface:传输中断给core

ITS:用来解析LPI中断

其中,cpu interface是实现在core内部的,distributor,redistributor,ITS是实现在gic内部的。

cpu interface和gic的redistributor通信,通过AXI-Stream协议,来实现通信。

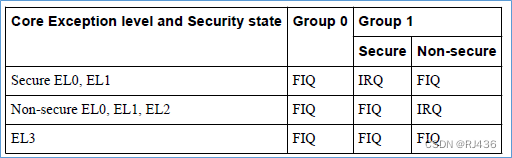

二、中断分组

gicv3,将中断分成了2个大组,group0和group1。

group0:提供给EL3使用

group1:又分为2组,分别给安全中断和非安全中断使用

如下图所示:

以下是IRQ,FIQ与组的对应关系。

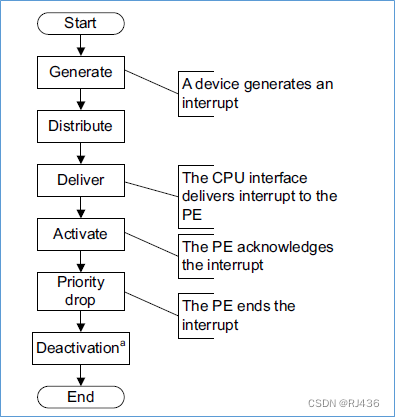

中断生命周期,如下图所示:

generate:外设发起一个中断

distribute:distributor对收到的中断源进行仲裁,然后发送给对应的cpu interface

deliver:cpu interface将中断发送给core

activate:core通过读取 GICC_IAR 寄存器,来对中断进行认可

priority drop: core通过写 GICC_EOIR 寄存器,来实现优先级重置

deactivation:core通过写 GICC_DIR 寄存器,来无效该中断

这个中断生命周期,和gicv2的中断生命周期是一样的。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!