芯片验证入门踩坑指南(1)

2024-01-08 07:09:16

因为一些原因,从华为数通C软件开发到海思这边做芯片验证,快一个月,说下一些心得与体会:

如何快速上手:

因为项目非常赶,几乎没有脱产学习时间,就是直接干项目,一开始不需要知道原理,熟悉基本的System Verilog语法和了解简单的UVM验证方法学就可以上手开始验证了,只需要关注自己需要做的,以及结果什么是对的,什么是错的就可以了,具体细节慢慢熟悉。

一些需要注意的点:

验证其实已经很自动化了,脚本都是现成的,只需要根据指导书按对应格式提取验证寄存器表或者一些固定格式的数据,导入用例,运行脚本即可,所以不用担心,熟悉一两次就很顺利了

目前遇到的难点:

验证出问题后,定位是自己的验证环境问题还是设计人员的问题,如果是设计人员问题,最好是要找到错误的点比如某某寄存器接错这种比较精确的点,防止扯皮,这个对于新手来说还是比较困难的。

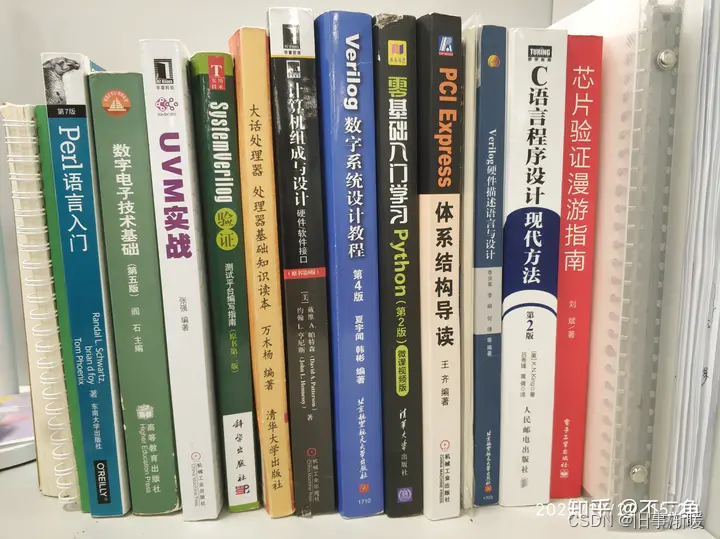

如果我提前做准备的话着重在哪些方面?

1.System Verilog语法熟悉

2.芯片相关的概念:寄存器、时钟、中断、复位等等

3.Verdi等仿真相关工具使用

4.Linux环境下开发技能

5.验证方法学概念

再过一个月再更新下

文章来源:https://blog.csdn.net/m0_46663240/article/details/135447543

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!