孩子都能学会的FPGA:第三十二课——用FPGA实现一个通用的SPI主机发送模块

(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

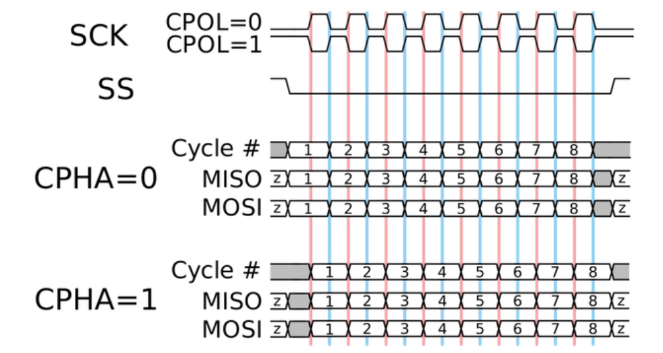

上节课我们实现了CPOL=0和CPHA=0的SPI主机的发送,现在我们要做一个通用的SPI主机的发送,就是支持POL=0/1和CPHA=0/1的4种组合情况,通过参数进行传递的方式选择4种不同的模式。仔细看一下下图,MOSI的第1个数据是发送数据的第1位,由第1个数据到第2个数据的变化都是在半个SCK的时钟后,也就是说设计FPGA的时候,刚开始的前半个周期的SCK的变化不会引起MOSI的变化,最后半个周期的SCK的变化也不会引起MOSI的变化,对于N位数据的传输,FPGA开始的时候发送最高位,后续只需要把数据左移N-1次,就可以完成N位数据的串行发送,所以移位操作是N-1次。

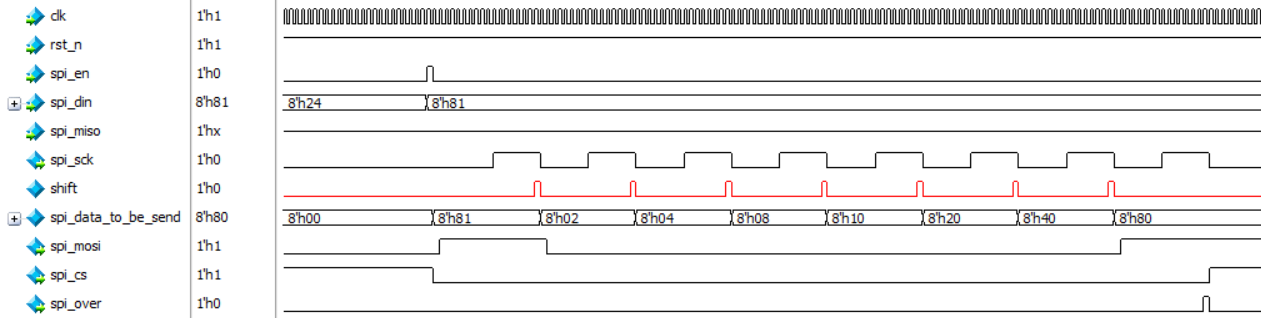

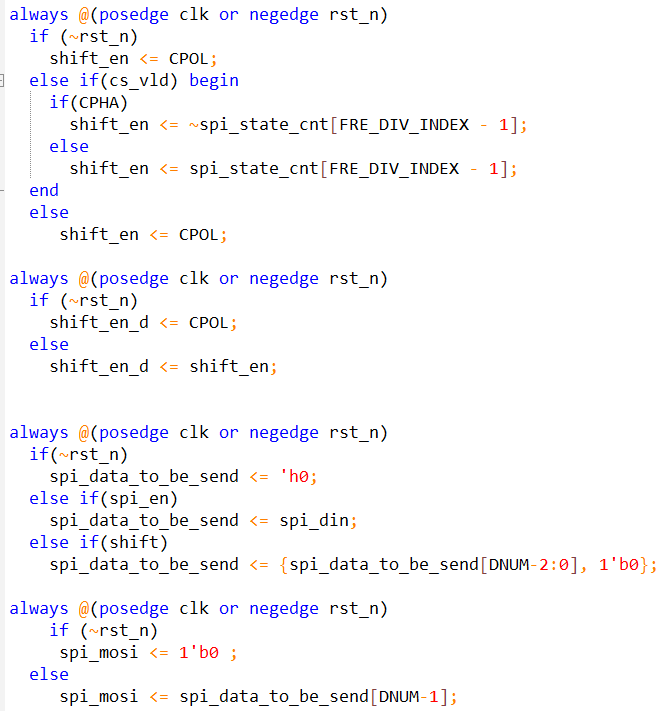

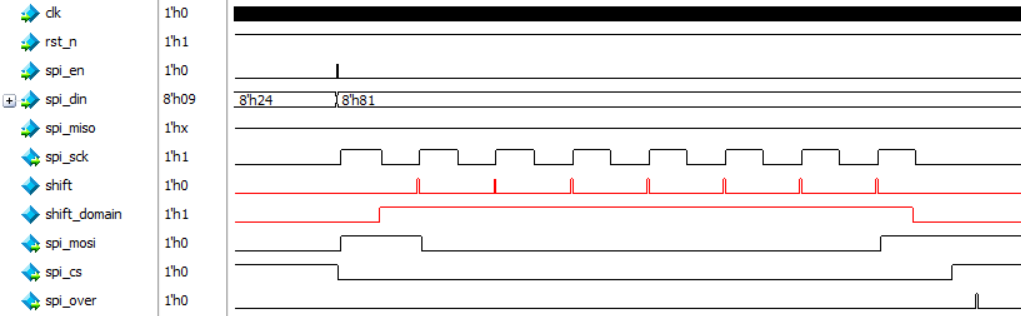

以上节课的为例,CPOL=0和CPHA=0,仿真波形如下所示,shift用来标识何时MOSI的信号进行变化。SPI的salve端会在SCK的上升沿采集数据,能够采集正确。

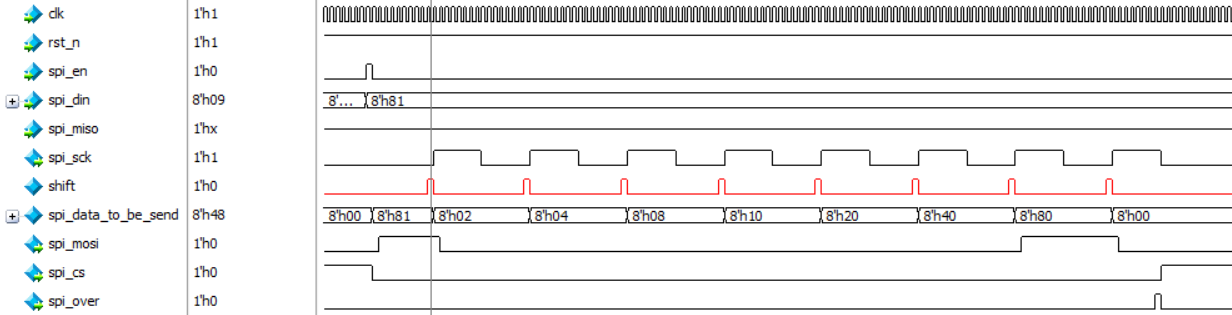

如果上节课的代码直接改成CPOL=0和CPHA=1,仿真波形如下,shift会在开始的位置多了一次使能,造成数据多移位一次,SPI的salve端会在SCK的下升沿采集数据,很明显采集不到正常的数据,从而数据传输错误。

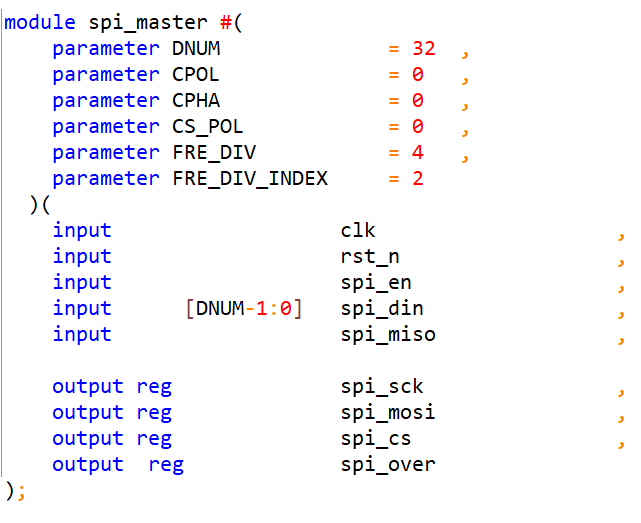

下面我们开始SPI通用主机发送模块的设计,主要改动是增加了三个参数CPOL,CPHA和CS_POL,CPOL定义了SCLK时钟线空闲状态时的电平,CPHA定义了数据位相对于时钟线的时序,CS_POL定义了使能信号的电平,就是spi_cs信号是高电平有效还是低电压有效。

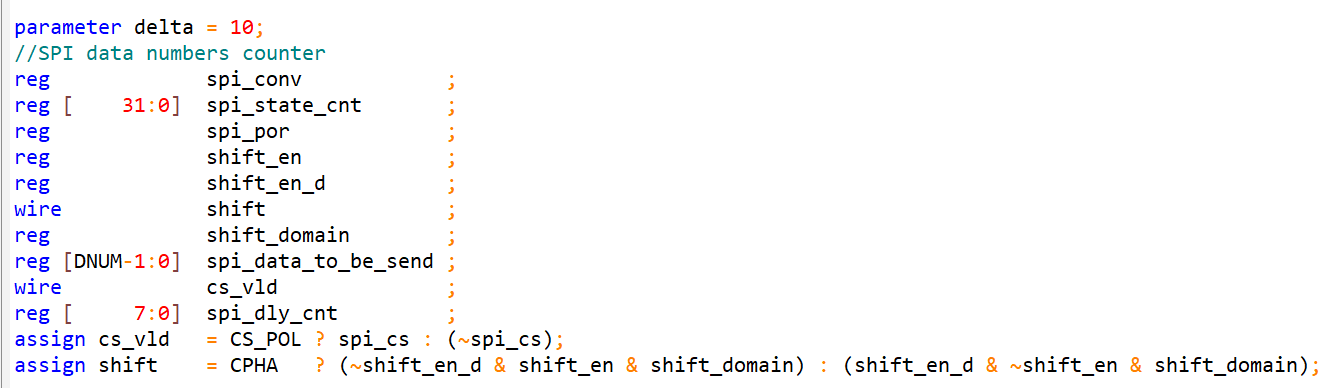

定义了一个delta的参数,是一次SPI通信后过多常长时间将spi_over信号使能,上节课是直接使能的,本节课可以通过参数进行控制。和上节课最大的区别是定义了shift_domain,在该信号使能的情况下数据才可以发送,主要用来控制shift信号在开始或者结束的位置多一次触发。shift是在上升沿触发还是在下降沿触发通过产生CPHA控制,spi_cs信号通过参数CS_POL来控制是高电平有效还是低电平有效。

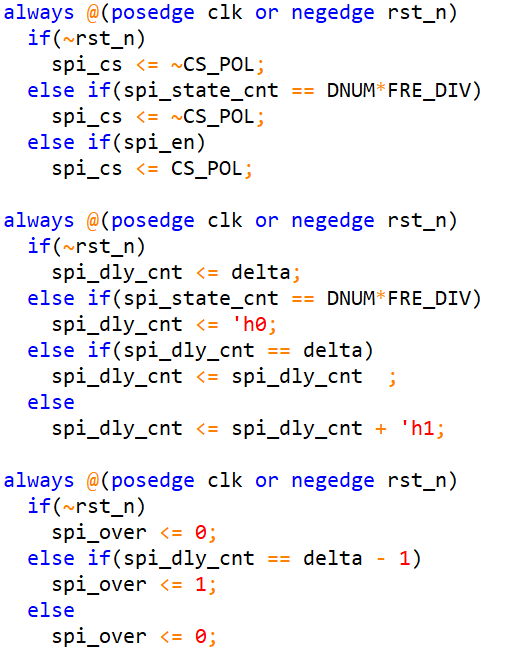

和上节课不同的是spi_cs信号和spi_over信号,如下所示。

通过参数CPOL来控制时钟在空闲状态下的电平,同时设置了数据移位的shift_domain,在SPI开始的前半个spi_sck和最后的半个spi_sck周期内不允许数据移位。

最后通过参数CPHA来控制spi_mosi上的信号是在spi_sck时钟的上升沿变化还是时钟的下降沿变化。

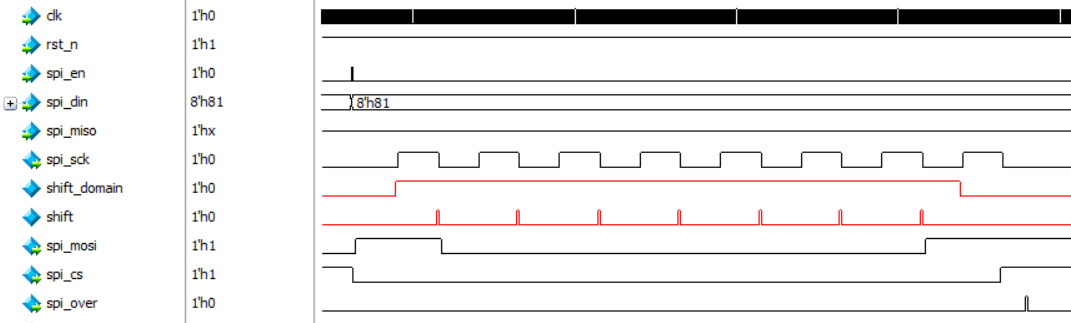

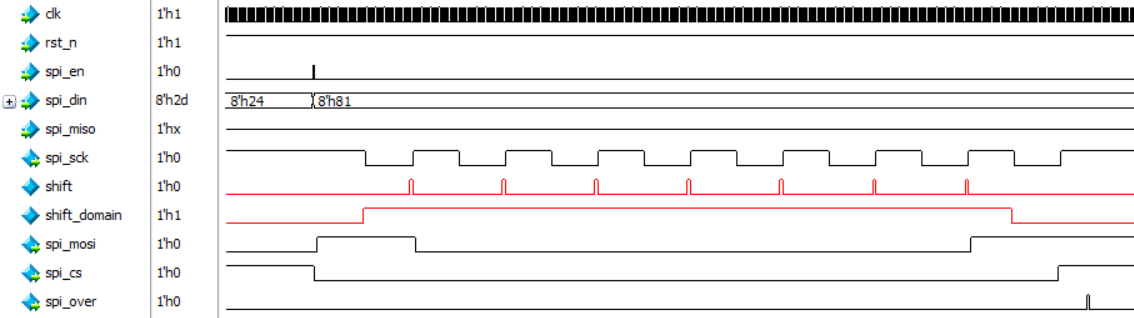

最后新建仿真的tb文件,用随机数进行仿真,其中CPOL=0,CPHA=0时的仿真波形如下,符合设计要求。

CPOL=1,CPHA=0的仿真波形如下,符合设计要求。

CPOL=0,CPHA=1的仿真波形如下,符合设计要求。

CPOL=1,CPHA=1的仿真波形如下,符合设计要求。

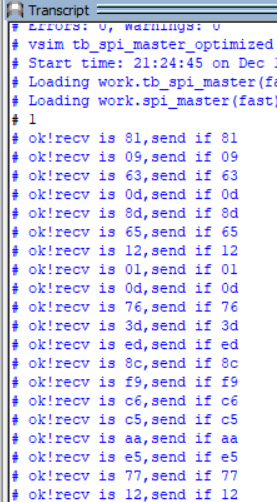

查看modelsim的Transcript窗口,spi_master发送的数据和spi_slave接收的数据一致,设计功能正常。

上述的SPI通用主机发送模块仅仅需要根据实际情况修改参数就可以适用于绝大多数SPI接口的主机通信,通用性非常好。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!