RV CORE梳理

2023-12-20 21:49:37

CACHE Register Definitions

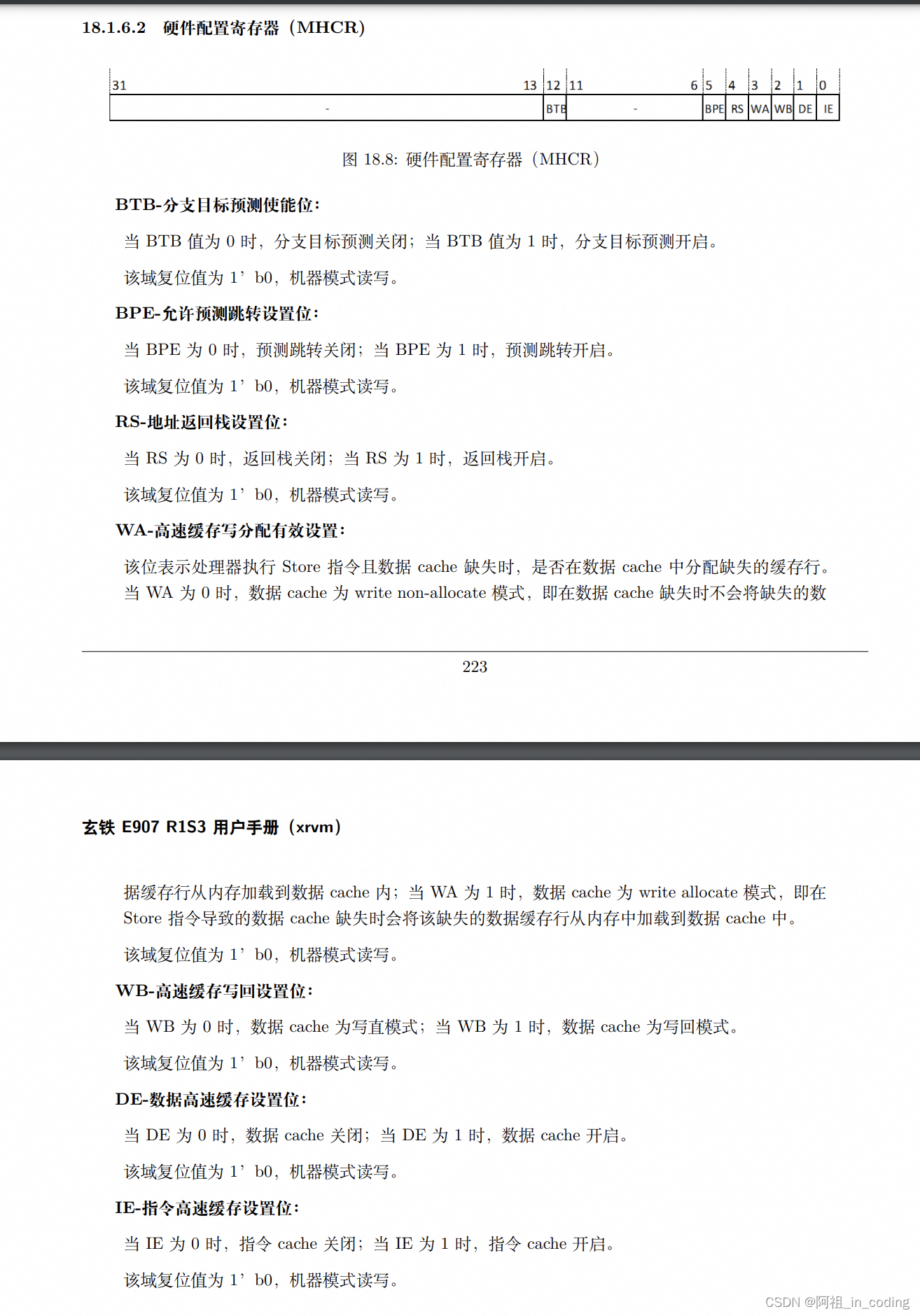

#define CACHE_MHCR_L0BTB_Pos 12U /*!< CACHE MHCR: L0BTB Position */

#define CACHE_MHCR_L0BTB_Msk (0x1UL << CACHE_MHCR_L0BTB_Pos) /*!< CACHE MHCR: WA Mask */

#define CACHE_MHCR_BPE_Pos 5U /*!< CACHE MHCR: BPE Position */

#define CACHE_MHCR_BPE_Msk (0x1UL << CACHE_MHCR_BPE_Pos) /*!< CACHE MHCR: BPE Mask */

#define CACHE_MHCR_RS_Pos 4U /*!< CACHE MHCR: RS Position */

#define CACHE_MHCR_RS_Msk (0x1UL << CACHE_MHCR_RS_Pos) /*!< CACHE MHCR: RS Mask */

#define CACHE_MHCR_WA_Pos 3U /*!< CACHE MHCR: WA Position */

#define CACHE_MHCR_WA_Msk (0x1UL << CACHE_MHCR_WA_Pos) /*!< CACHE MHCR: WA Mask */

#define CACHE_MHCR_WB_Pos 2U /*!< CACHE MHCR: WB Position */

#define CACHE_MHCR_WB_Msk (0x1UL << CACHE_MHCR_WB_Pos) /*!< CACHE MHCR: WB Mask */

#define CACHE_MHCR_DE_Pos 1U /*!< CACHE MHCR: DE Position */

#define CACHE_MHCR_DE_Msk (0x1UL << CACHE_MHCR_DE_Pos) /*!< CACHE MHCR: DE Mask */

#define CACHE_MHCR_IE_Pos 0U /*!< CACHE MHCR: IE Position */

#define CACHE_MHCR_IE_Msk (0x1UL << CACHE_MHCR_IE_Pos) /*!< CACHE MHCR: IE Mask */

#define CACHE_INV_ADDR_Pos 5U

#define CACHE_INV_ADDR_Msk (0xFFFFFFFFUL << CACHE_INV_ADDR_Pos)

文章来源:https://blog.csdn.net/qq_38537501/article/details/135117430

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!