STM32 AD5693R开发

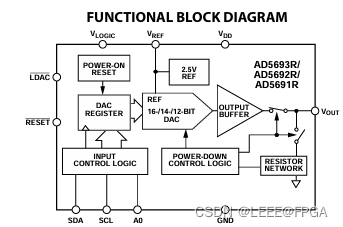

0 AD5693R介绍

1 IIC介绍

2线串行总线协议的工作方式如下:

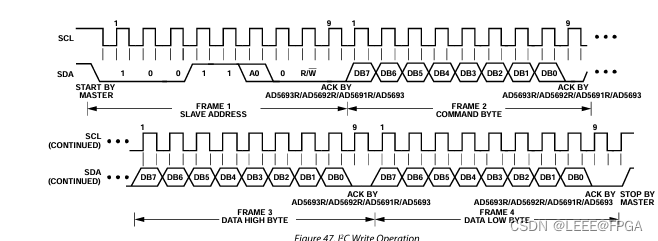

1.当SCL为高电平时,当SDA线路发生高到低转换时,主机通过建立启动条件来启动数据传输。以下字节是地址字节,它由 7 位从地址组成。与发送地址对应的从地址在第 9 个时钟脉冲期间将 SDA 拉低(这称为确认 (ACK) 位)进行响应。在此阶段,总线上的所有其他设备保持空闲状态,而所选设备等待数据写入或读取其移位寄存器。

2. 数据通过串行总线以九个时钟脉冲(八个数据位后跟一个确认位)的顺序传输。SDA 线路上的转换必须发生在 SCL 的低期,并在 SCL 的高期保持稳定。

3. 读取或写入所有数据位后,建立停止条件。在写入模式下,主机在第 10 个时钟脉冲期间将 SDA 线拉高以建立停止条件。在读取模式下,主机对第九个时钟脉冲发出不确认(即SDA线保持高电平)。然后,主机在第 10 个时钟脉冲之前将 SDA 线调至低电平,然后在第 10 个时钟脉冲期间将 SDA 线调至高电平,以建立停止条件。

2 IIC ADDRESS

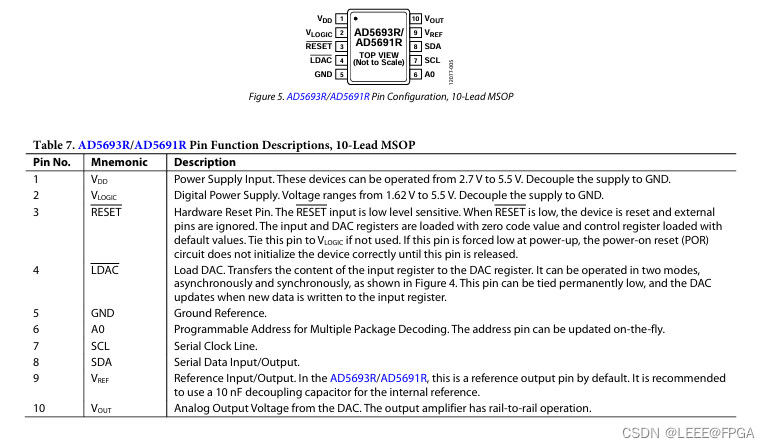

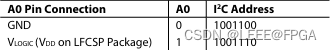

AD5693R/AD5692R/AD5691R/AD5693具有7位从机地址。这五个 MSB 是 10011。A0 地址引脚和 LSB 的状态设置的倒数第二位为 0。对 A0 进行硬连线更改的能力使用户能够在一条总线上拥有两个这样的设备,如表 11 所示。此外,引脚可以在开始传输之前更新,通过将引脚连接到GPIO或多路复用器,允许同一总线中的多个器件。

3 WRITE OPERATION

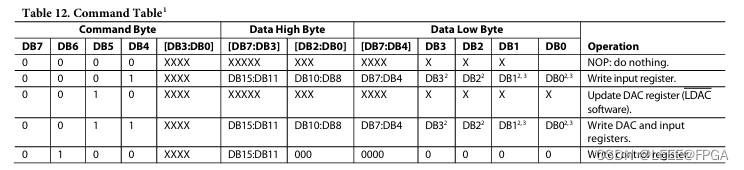

写入AD5693R/AD5692R/AD5691R/AD5693时,用户必须以启动条件开头,后跟地址字节(R/W = 0),之后DAC确认它已准备好通过将SDA拉至低电平来接收数据,如图47所示。 AD5693R/AD5692R/AD5691R/AD5693需要一个命令字节来控制各种DAC功能(见表12)和两个DAC数据字节。所有这些数据字节均由AD5693R/AD5692R/AD5691R/AD5693确认。停止条件如下。

Write Input Register

输入寄存器允许为DAC寄存器预加载一个新值。从输入寄存器到DAC寄存器的转换可由硬件、LDAC引脚或使用命令2的软件触发。 如果将新数据加载到DAC寄存器中,则DAC寄存器会自动覆盖输入寄存器。

Update DAC Register

该命令将输入寄存器的内容传输到DAC寄存器,从而更新VOUT引脚。串行写入中包含的数据将被忽略。 此操作等同于软件 LDAC。

Write DAC Register

此命令在写入操作完成后更新 DAC 输出。输入寄存器使用DAC寄存器值自动刷新。

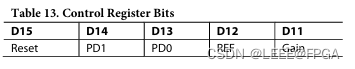

Write Control Register

控制寄存器用于设置省电和增益功能。它还用于启用/禁用内部基准电压源并执行软件复位。有关控制寄存器功能,请参见表 13。

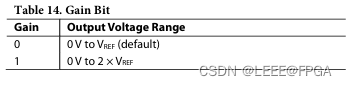

Gain Bit

增益位选择输出放大器的增益。表14显示了输出电压范围与增益位状态的对应关系。

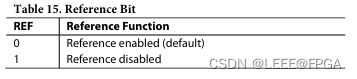

REF Bit

仅在 AD5693R/AD5692R/AD5691R 中,片内基准电压源默认在上电时导通。通过在控制寄存器中设置软件可编程位DB12,可以打开或关闭此基准。表 15 显示了位的状态如何与操作模式相对应。

为了降低功耗,如果器件处于省电模式,建议禁用内部基准。

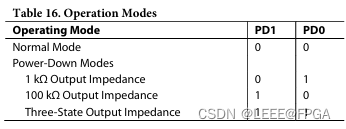

PD0 and PD1 Bits

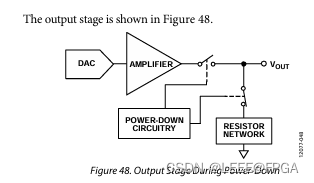

AD5693R/AD5692R/AD5691R/AD5693包含两种独立的工作模式,可通过写入控制寄存器进行访问。 在正常模式下,输出缓冲器直接连接到VOUT引脚。 在省电模式下,输出缓冲器在内部禁用,VOUT引脚输出阻抗可选择至已知值,如表16所示。

在省电模式下,该器件禁用输出缓冲器,但不禁用内部基准。为了实现最大的节能效果,建议禁用内部基准电压源。 禁用内部基准电压源和输出缓冲器会导致电源电流在5 V时降至2 μA。

当省电模式被激活时,输出放大器被关断。但是,除非内部基准电压源断电(使用控制寄存器中的位DB12),否则偏置发生器、基准电压源和电阻串保持导通状态。电源电流在5 V时降至2 μA。在省电模式下,DAC寄存器的内容不受影响,DAC寄存器可以继续更新。当VDD = 5 V时,退出关断所需的时间通常为4 μs,如果基准电压源被禁用,则为600 μs。

Reset Bit

AD5693R/AD5692R/AD5691R/AD5693控制寄存器包含一个软件复位位,用于将DAC复位至零电平,并将输入、DAC和控制寄存器复位至默认值。 通过将控制寄存器中的RESET位设置为1来启动软件复位。软件复位完成后,复位自动清除为0。

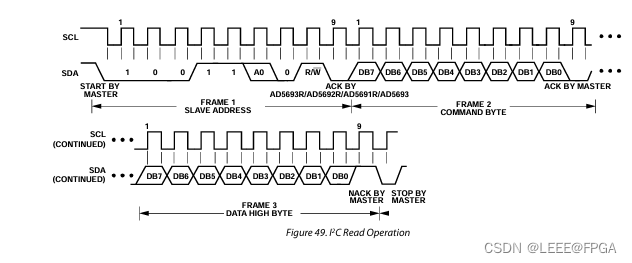

READ OPERATION

当从AD5693R/AD5692R/AD5691R/AD5693 DAC读回输入寄存器时,用户以地址字节(R/W = 1)开头,之后DAC通过拉低SDA来确认它已准备好接收数据。然后从DAC读取包含输入寄存器内容的2字节数据,如图49所示。来自主节点的 NACK 条件后跟 STOP 条件完成读取序列。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!