基于Xilinx bitslice原语实现delay可调整的MIPI DPHY

背景

? ? ? ? Xilinx自带的DPHY在1.5G时无法调整data line的delay值,在需要调整数据线延时的场景可使用文中方案,且有较少的资源占用。使用IBUFDS_DPHY,BITSLICE,BITSLICE_CONTROL实现MIPI DPHY。包含1条clock lane,4条 data lane。参考《UG571 ultralscale selectio》。

1 时钟域

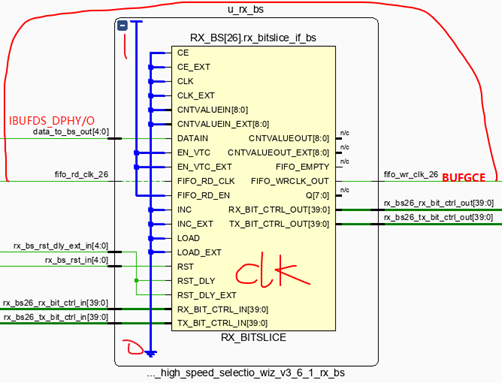

? ? ? ?随路时钟由时钟RX_BITSLICE_0转给BITSLICE_CONTROL,根据设置是否偏移90°(DDR时钟数据边沿对齐时需要),再转入所有数据RX_BITSLICE用于采样;同时时钟RX_BITSLICE_0给出字节时钟,用于后续逻辑处理用;

????????PLL_CLK:1000M仅用于CONTROL的校准、延时控制;

????????RIU_CLK用于访问CONTROL内部的64个reg,实践中并未访问;

? ? ? ?CLK:延时控制接口的参考时钟,延时调整也有时序要求,tap的步进需要通过两条数据线计算得到。

? ? ? ?BISC与RIU接口不需要直接操作,仅用延时接口调整延时即可。

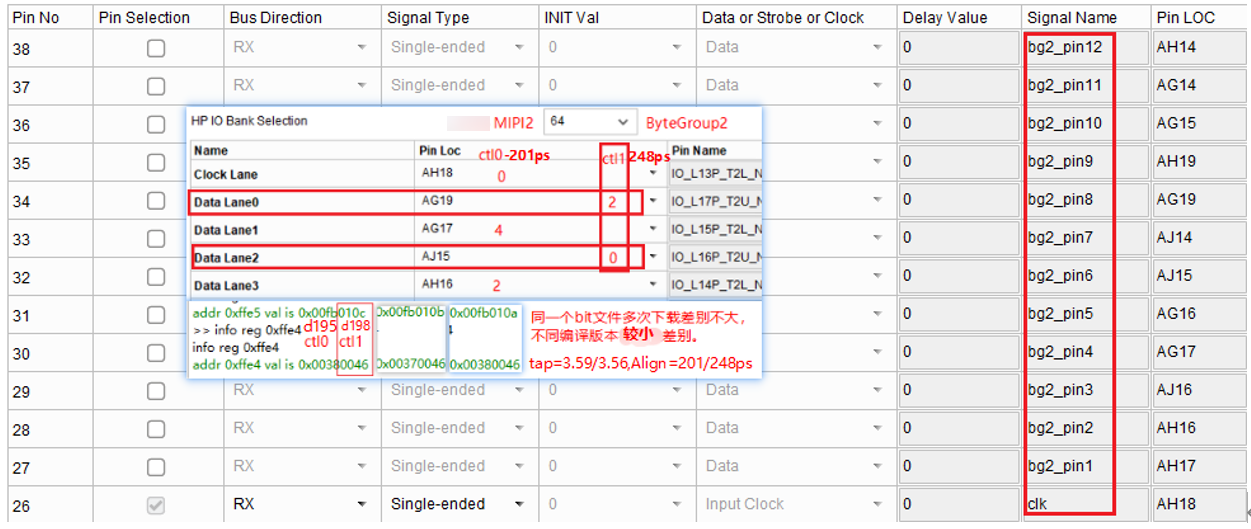

2 管脚

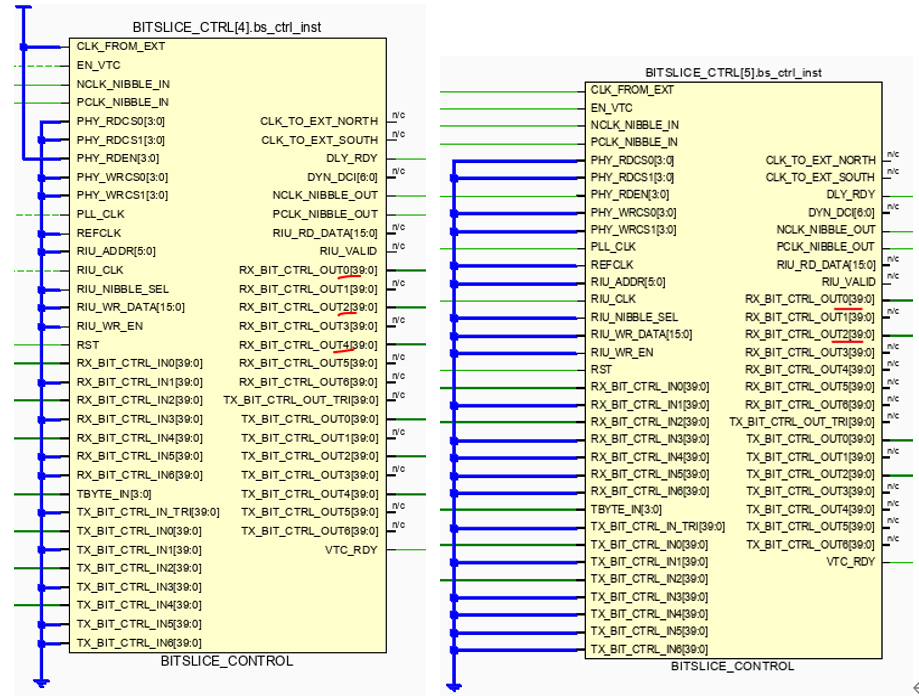

? ? ? ? 一个Bank共52pins,分为4组字节(每字节13pins),每字节又分为上下两个半字节(6,7pins).每个半字节对应一个CONTROL(有7个控制口对应7个IO),使用时按照管脚顺序一一对应,差分管脚在CTL上仅使用p脚,n脚空出。故每个byte组中,MIPI的clk+/-,data0+/-,data1+/- 占6个pin0~5对应在第一个bitslice_control上,data2+/-, data3+/-占4个pin6~9对应在第二个bitslice_control上。

? ? ? ?若MIPI使用了两个半字节管脚,则要使用两个CONTROL,且接收随路时钟所在的CTL需要把PCLK/NCLK转发给另一个CTL(PCLK_NIBBLE_OUT)。

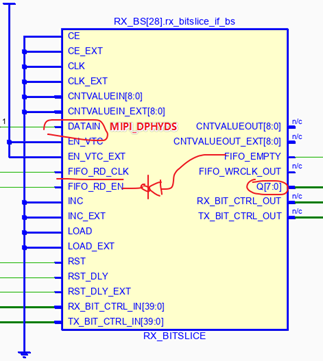

3 slice原语模块pins

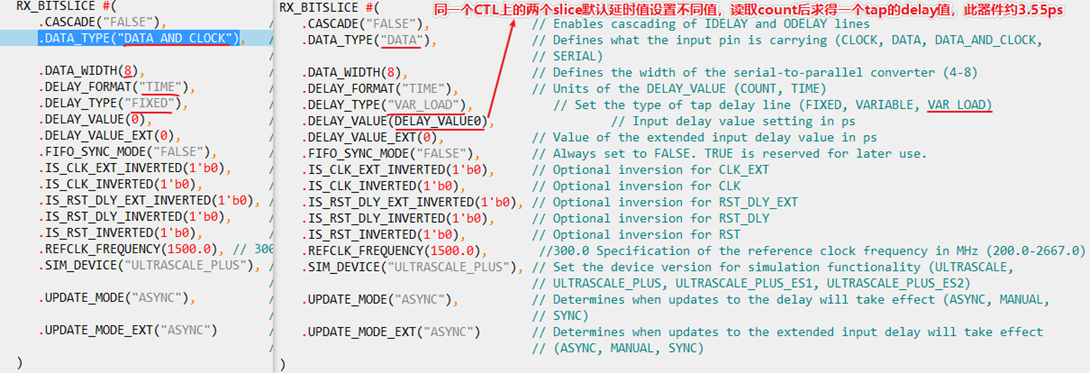

clock RX_BITSLICE配置为.DATA_TYPE("DATA_AND_CLOCK"),data RX_BITSLICE配置为 .DATA_TYPE("DATA ").

clk slice的FIFO_WRCLK_OUT输出byte_clk,加BUFG后用于读取slice自带深度为8的FIFO;

每个slice的FIFO_EMPTY信号取反后用作读FIFO使能;

40bits信号用户不用关心,按照收对发连接两个CTL即可,未使用的接0。

第二个CTL中开启接收来自第一个CTL的采样时钟PCLK/NCLK.

多个bitslice对其的建议:

To ensure that all RX bit slices start aligned, the rx_clk_in (FIFO_RD_CLK) [(rx_clk_in in the above example)] should be stopped until the RX VTC_RDY signal is asserted(对齐使用的1500M,rd_clk要上位机开启clk才会有,实践中后给出clk仍然会出现不对齐,待clk出现后复位所有slice能明显改善)

为输入clk和生成clk添加约束:

create_clock -name rx_clk -period 2.000 -waveform {0.000 1.000} [get_ports rx_clk_in] create_generated_clock -divide_by 2 -source [get_ports rx_clk_in] -name fifo_wrclk rx_clock_bitslice_inst/FIFO_WRCLK_OUT

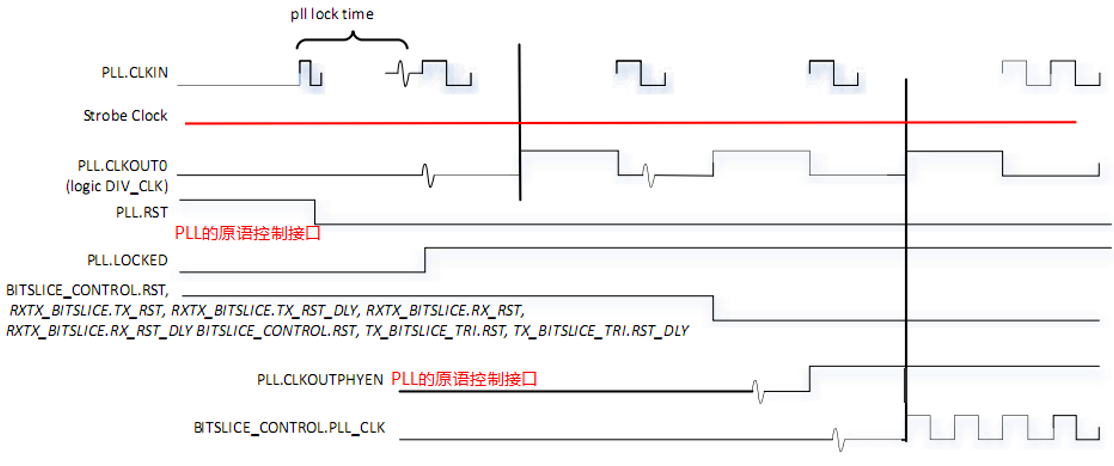

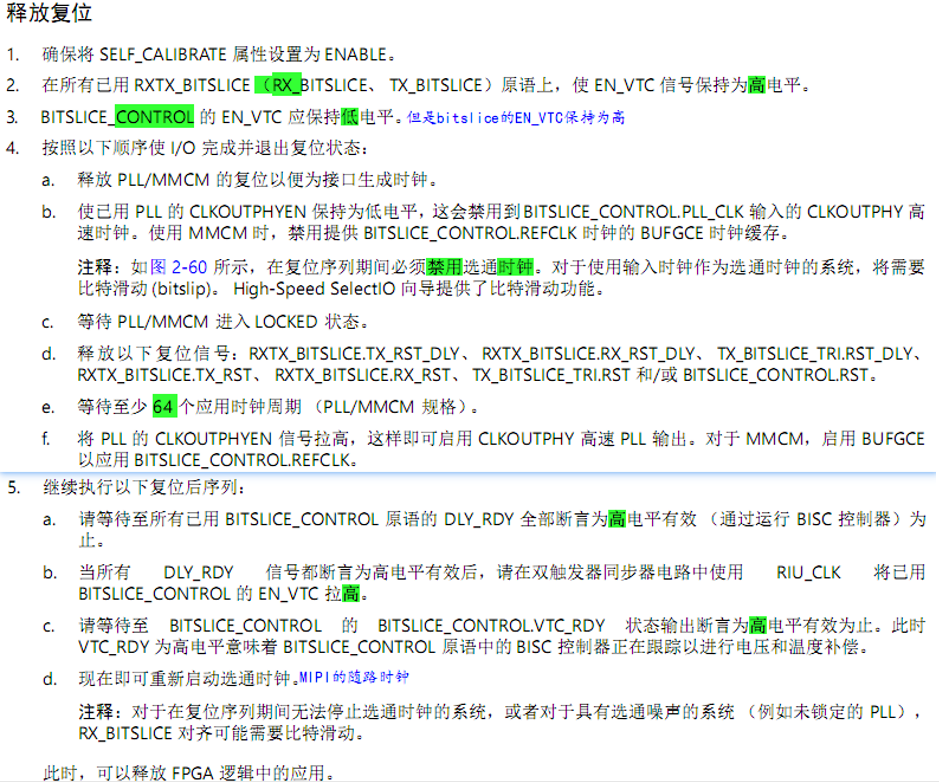

4 复位逻辑

?????

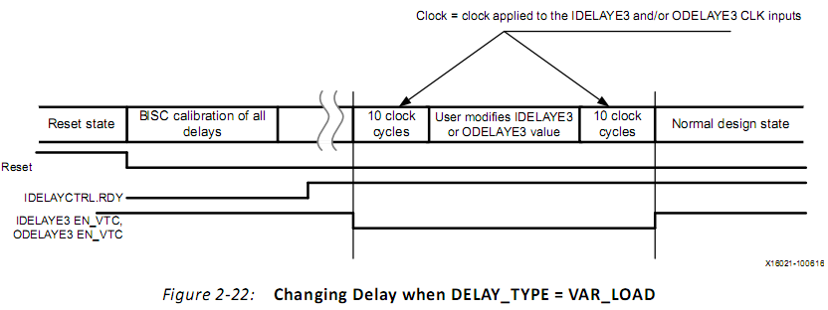

5?增加delay

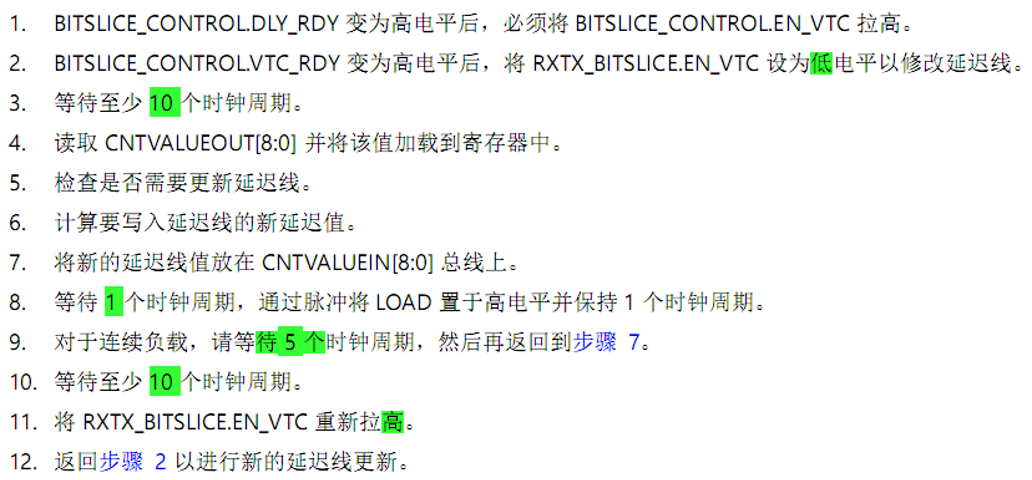

load_var步骤:

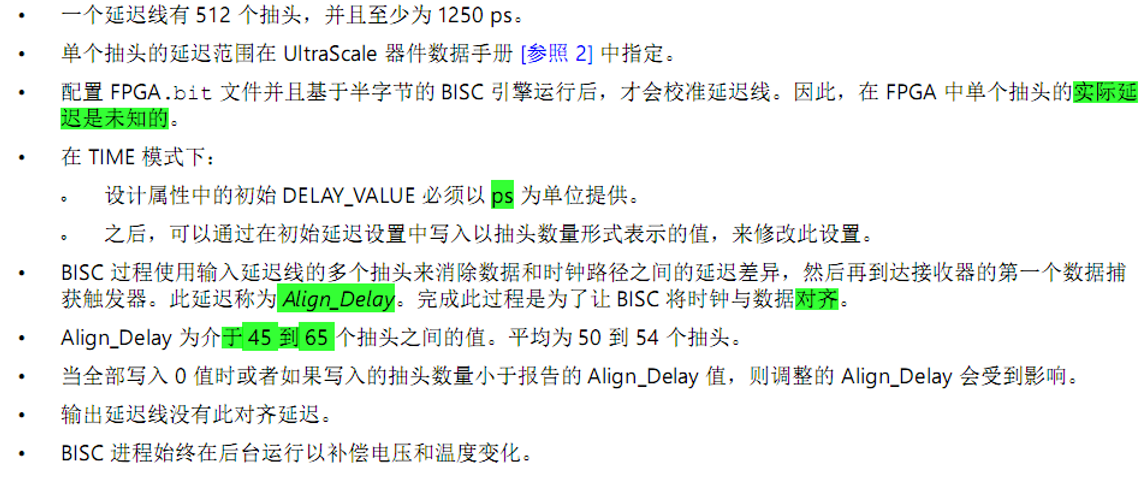

须知:

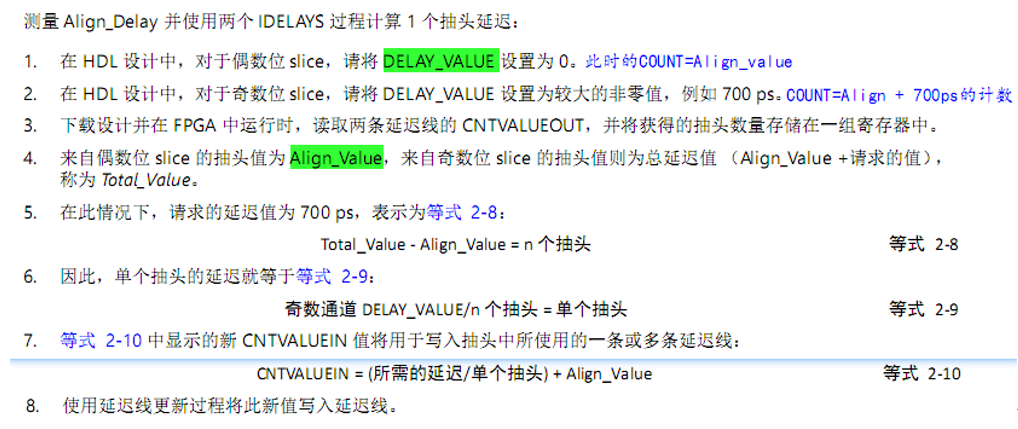

计算tap步骤:

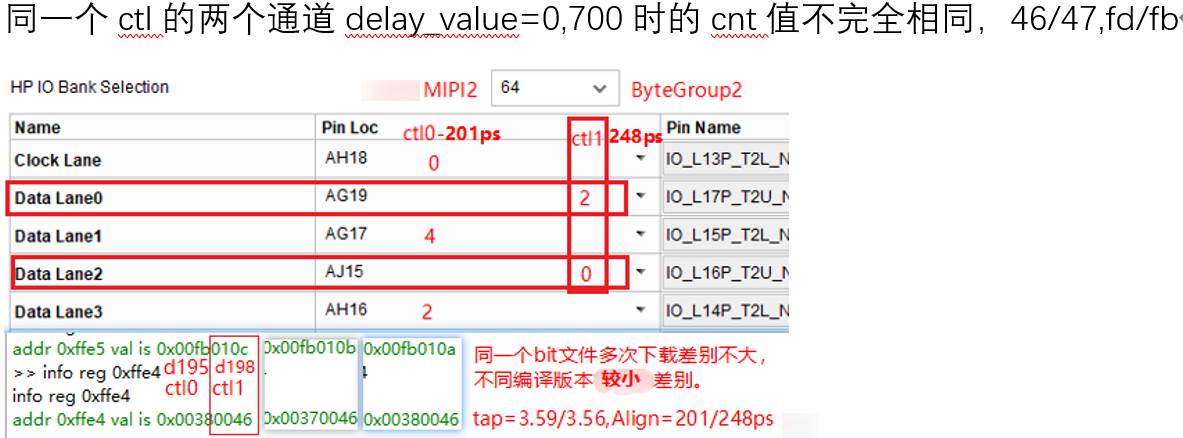

第一个带clk的control默认延时小0x38=201ps,第二个CTL默认延时大0x46=248ps.

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!