Verilog置换处理脚本

2023-12-28 02:39:58

一、介绍

在Verilog中的置换处理,为将一个数据的数据位按照某种规则进行重新排列。

以DES算法的初始置换为例

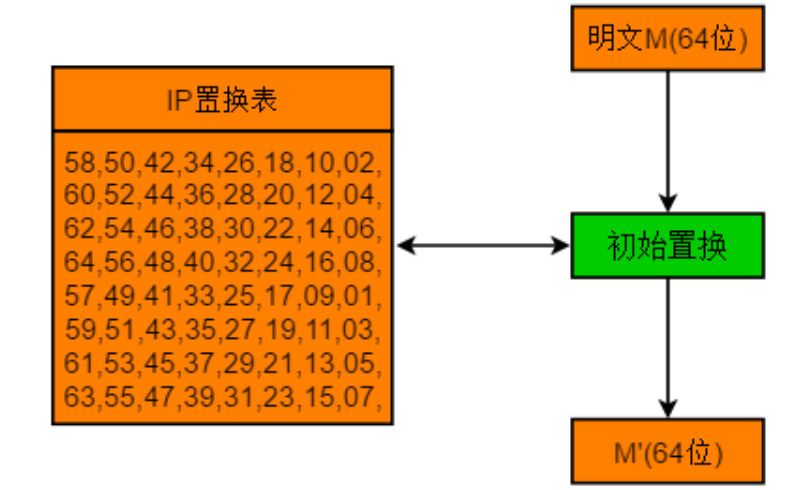

初始置换将64比特的明文,按照初始置换表进行置换,得到一个乱序的64bit明文组。

初始置换表如下:

第一个数58表示,将明文M的第58位放置在第1位。

二、脚本

- config.txt文件

data 14 17 11 24 1 5 3 28 15 6 21 10 23 19 12 4 26 8 16 7 27 20 13 2 41 52 31 37 47 55 30 40 51 45 33 48 44 49 39 56 34 53 46 42 50 36 29 32- 第一行为变量的名称

- 接下来的行为置换表的内容

- main.py

def get_varinfo(config_path:str)->[str,[]]: f = open(config_path,"r") varname = f.readline().strip() varidxs = [] for line in f.readlines(): for idx in line.split(): varidxs.append(int(idx.strip())) f.close() return [varname,varidxs] def output_expression(varname:str,varidxs:[int],linenum=8,databit=2)->None: print("{") for idx in range(len(varidxs)-1): print(("{}[{:"+str(databit)+"}],").format(varname,varidxs[idx]),end=' ') if (idx+1)%linenum == 0 : print("") print(("{}[{:"+str(databit)+"}]").format(varname,varidxs[len(varidxs)-1])) print("};") def main(): varname , varidxs = get_varinfo("./config.txt") output_expression(varname,varidxs) if __name__ == "__main__": main()

文章来源:https://blog.csdn.net/first_bug/article/details/135256425

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!