vivadoQoR 建议报告 RTL 代码更改示例2

2023-12-13 04:58:07

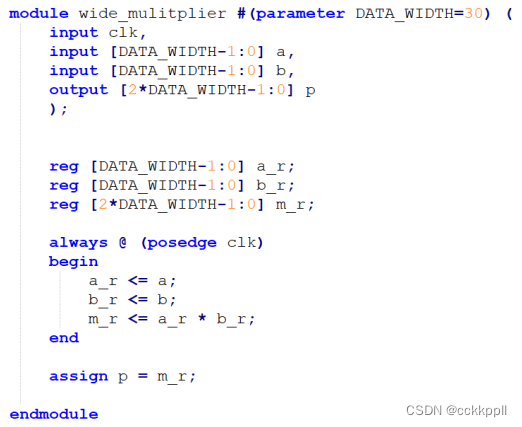

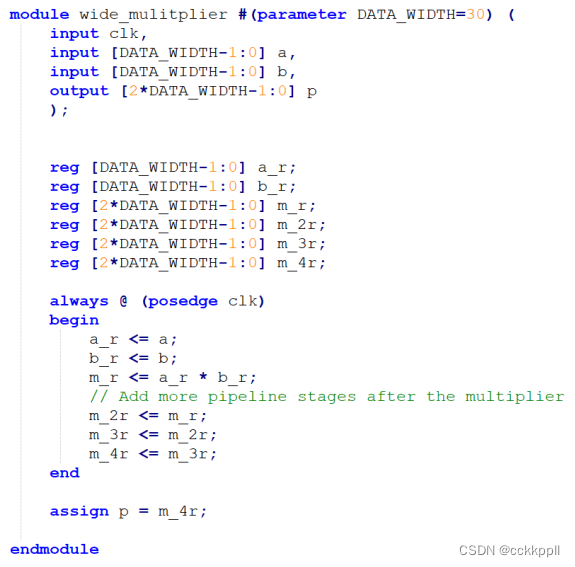

RQS_TIMING-202

:

添加额外流水打拍以拓宽倍频器

宽型倍频器

(

即给定架构中至少一个端口大于

DSP slice

所支持的最大宽度

)

需额外流水线以实现

DSP slice

的最大工作频率。流水线阶段的数量需根据所需宽度更改。通过在 RTL

中对宽型倍频器输出添加额外阶段

,

综合即可将其移至最优化位置以大幅简化重新编码。

修改前

修改后

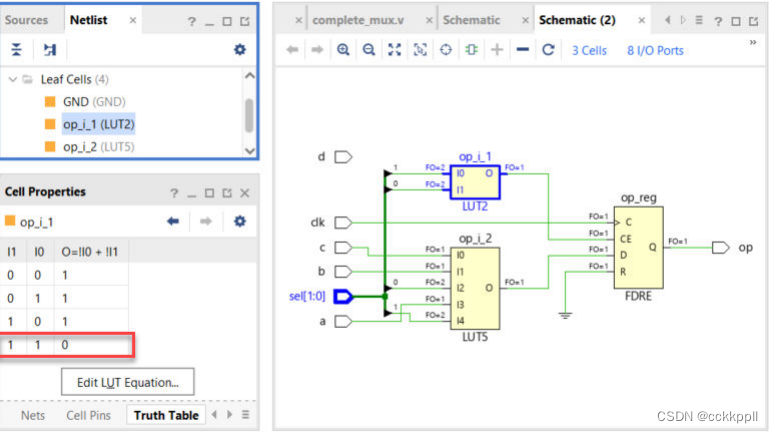

RQS_UTIL-10

:

Case

语句不完整导致控制集增加

当

case

语句不完整时

,

会强制输出记住用于推断时钟使能的先前状态。建议定义所有状态。对于其他状态

,

请将输出定义为先前使用的信号或者常量 1

或常量

0

,

以免增加逻辑。下图显示了当状态“11

”未定义时

,

CE LUT

的推断。

module incomplete_mux(

input clk,

input a,b,c,d,

input [1:0] sel,

output reg op

);

always @(posedge clk)

begin

case (sel)

2'b00 : op <= a;

2'b01 : op <= b;

2'b10 : op <= c;

default: ;

endcase

end

endmodule

修改后

module incomplete_mux(

input clk,

input a,b,c,d,

input [1:0] sel,

output reg op

);

always @(posedge clk)

begin

case (sel)

2'b00 : op <= a;

2'b01 : op <= b;

2'b10 : op <= c;

2'b11 : op <= a; // ADDED

default: ;

endcase

end

endmodule

文章来源:https://blog.csdn.net/cckkppll/article/details/134958409

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!