【FPGA】Verilog:编码器 | 实现 4 到 2 编码器

2023-12-17 19:59:10

0x00 编码器(Encoder)

编码器与解码器相反。当多台设备向计算机提供输入时,编码器会为每一个输入生成一个与设备相对应的信号,因此有多少比特就有多少输出,以数字形式表示输入的数量。

例如,如果有四个输入,就需要一个两位二进制数来表示 0 至 3,这样就有四个输出。编码器用于转换和标准化表格或格式、提高安全性、加快处理速度或压缩数据。

编码器的应用:文件压缩 在计算机上生成视频、图像和声音等数据时,编码器用于编码和压缩数据,以减少数据量。

| 解码器 | |||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||

0x01 4 到 2 编码器的实现

解释 4 到 2 编码器的结果和仿真过程。(包括真值表和 k 映射图的创建)

0x02 真值表

| 输入 | 输出 | ||||

| A | B | C | D | E0 | E1 |

| 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 |

0x03 卡诺图

| E0 | E1 |

|

|

|

0x04 代码演示

💬 Design source:

`timescale 1ns / 1ps

module enc(

input A,

input B,

input C,

input D,

output E0,

output E1

);

assign E0 = C | D;

assign E1 = B | D;

endmodule💬 Testbench:

`timescale 1ns / 1ps

module enc_tb;

reg A,B,C,D;

wire E0,E1;

enc u_enc (

.A(A ),

.B(B ),

.C(C ),

.D(D ),

.E0(E0 ),

.E1(E1 )

);

initial begin

A = 1'b0;

B = 1'b0;

C = 1'b0;

D = 1'b0;

end

always@(A or B or C or D) begin

A <= #10 ~A;

B <= #20 ~B;

C <= #40 ~C;

D <= #80 ~D;

end

initial begin

#160

$finish;

end

endmodule🚩 运行结果如下:

在实践中,实现的 4 到 2 编码器将来自解码器的输出作为输入,并将来自解码器的输入作为输出返回。换句话说,对于 4 位输入值,如果 A 是最高有效位(MSB),则对于输入值 0001,它将返回输出 11;对于输入值 0010,它将返回输出 10;对于输入值 0100,它将返回输出 01;对于输入值 1000,它将返回输出 00。

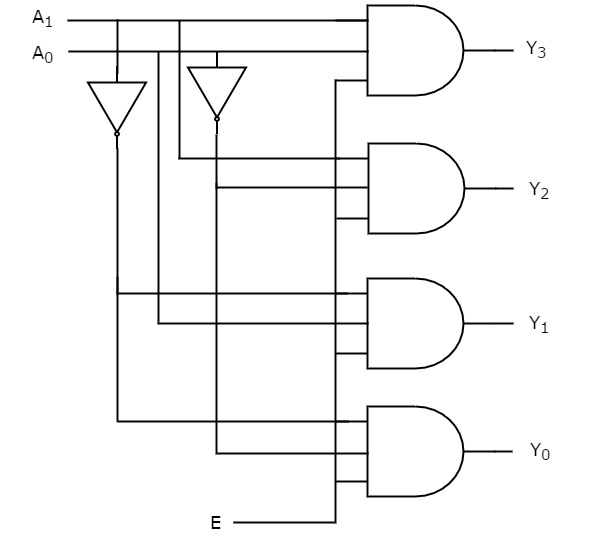

0x05 Schematic

📌 [ 笔者 ]? ????

📃 [ 更新 ]? ?2023.12.14

? [ 勘误 ]?? /* 暂无 */

📜 [ 声明 ]? ?由于作者水平有限,本文有错误和不准确之处在所难免,

本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料? Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |

文章来源:https://blog.csdn.net/weixin_50502862/article/details/135038969

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!