基于FPGA的视频接口之高速IO(CML)

2023-12-18 18:33:23

简介

????????本章节是对于高速IO接口应用的一个扩展,目前扩展为CML。

? ? ? ? CML(电流模式逻辑-即Current Mode Logic)。电路主要靠电流驱动,也是所有高速数据接口形式中最简单的一种,它的输入与输出的匹配集成在芯片内部,基本不需要外部端接,从而使单板硬件设计更简单、更简洁。CML其为LVDS的升级版本,但速度更快,速度最快可达到10G。

????????FPGA的高速IO接口GTX,可完美覆盖CML的速度范围。

应用

? ? ? ? 应用1:长距离传输视频数据;

? ? ? ? 应用2:传输高速数据。

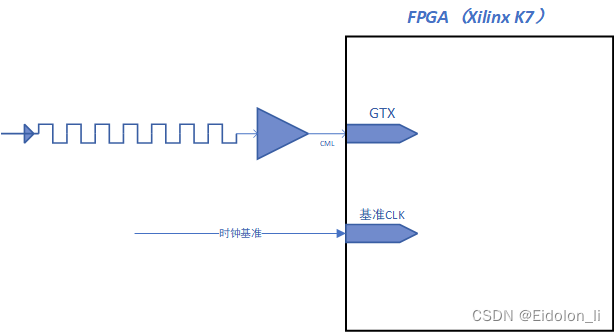

硬件框架

GTX实现物理层

? ? ?

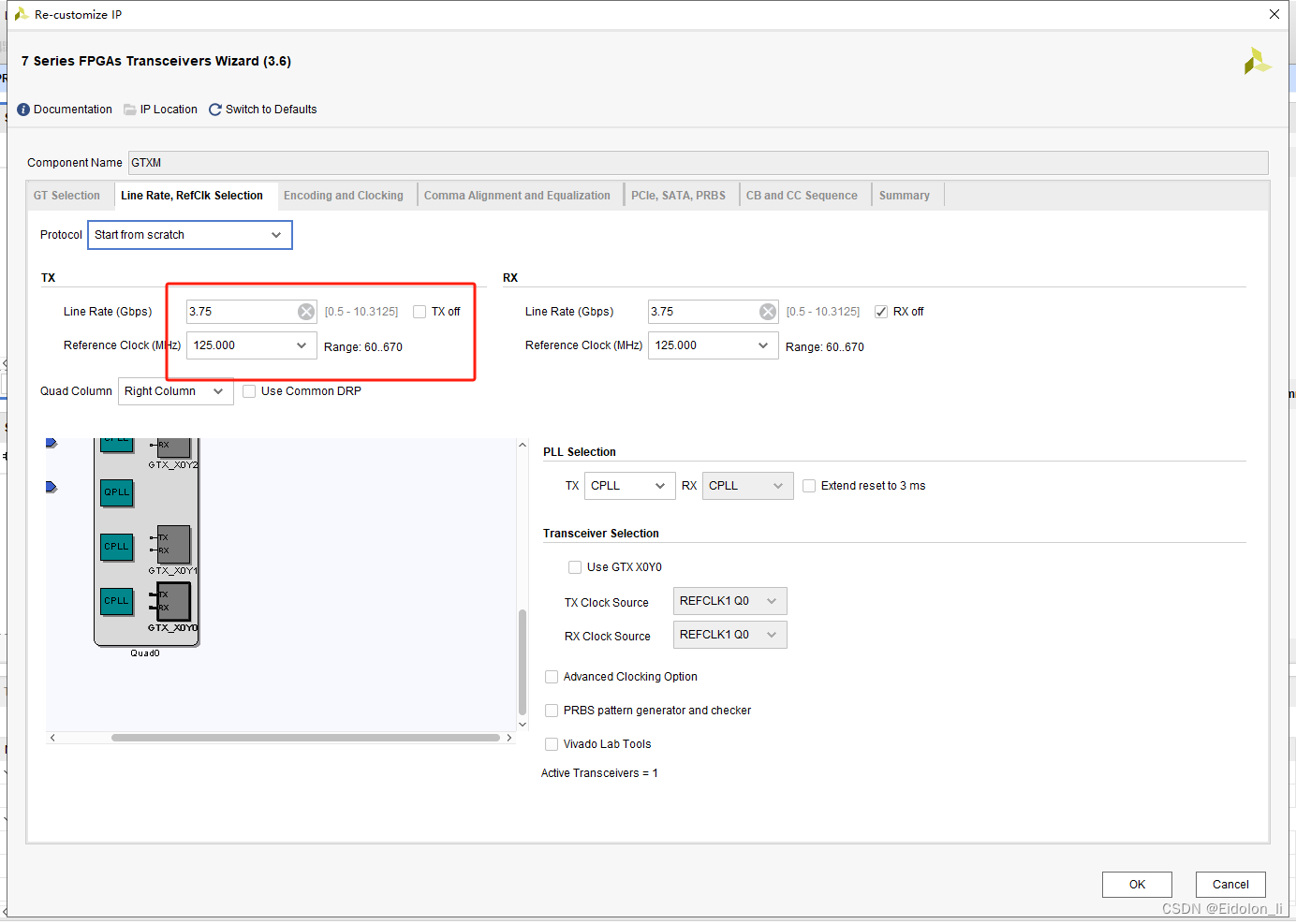

CML采用3.75Gbps速度,基准时钟采用125Mhz。

文章来源:https://blog.csdn.net/lihongfei_sky/article/details/135065569

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!