西南科技大学数字电子技术实验四(基本触发器逻辑功能测试及FPGA的实现)FPGA部分

2023-12-15 09:30:29

- 实验目的

1、掌握基本RS触发器、集成D触发器和JK触发器的逻辑功能及测试方法。

2、熟悉D触发器和JK触发器的触发方法。

3、熟悉用JK和D触发器构成其他功能触发器的方法。

4、学会用FPGA实现本实验内容。

- 实验原理

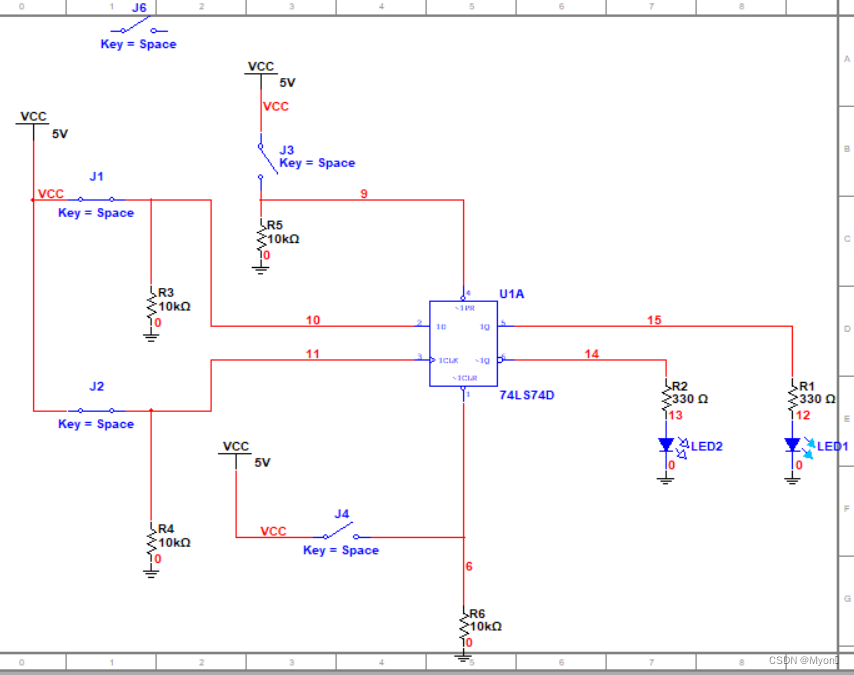

1、D触发器

Qn+1 = D

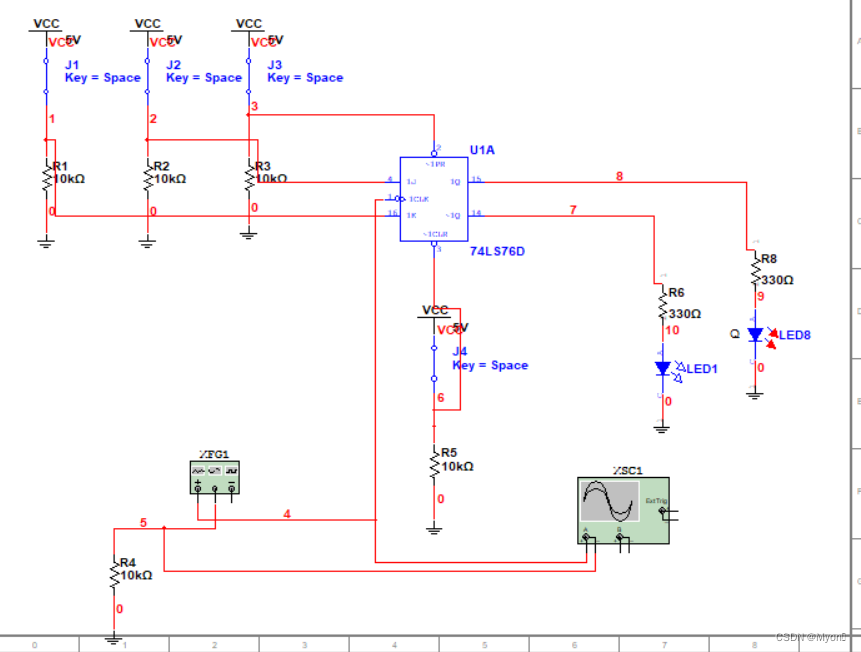

2、JK触发器

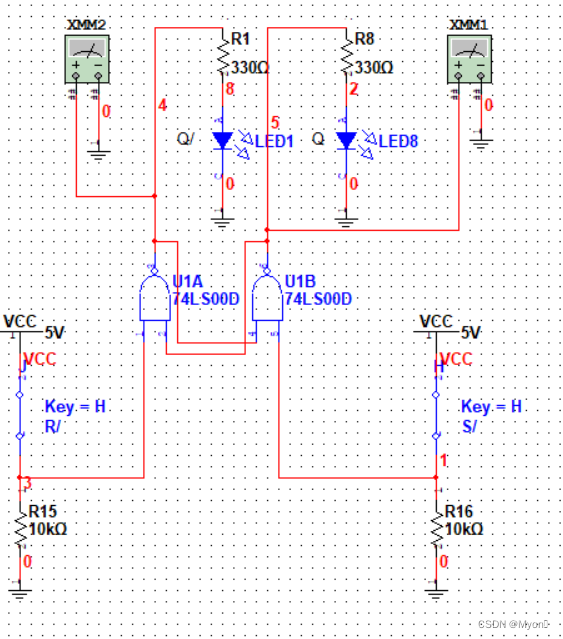

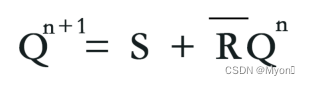

3、RS触发器

- 程序清单(每条语句必须包括注释或在开发窗口注释后截图)

提示:多个设计按以下格式(打印时删除)

(1)D触发器

原理代码

module d_chufa11

(

input rst,clk,d,set,

output reg q,

output wire qb

);

assign qb=~q;

always @ (posedge clk or negedge rst or negedge set)

begin

if(!rst)

q <= 1'b0;

else if(!set)

q <= 1'b1;

else

q<=d;

end

divide #

(

.WIDTH (32),

.N(12000000)

)

u1

(

文章来源:https://blog.csdn.net/Myon5/article/details/134919156

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!