Makefile

2023-12-14 21:41:51

Makefile在多文件功城中常常使用,了解其基本的规则是很有必要的。

基本结构

在一个 Makefile 中通常包含如下内容:

1.需要由 make 工具创建的目标体(target),通常是目标文件或可执行文件;

2.要创建的目标体所依赖的文件(dependency_file);

3.创建每个目标体时需要运行的命令(command)。

例如:

target: dependency_files // target为目标文件,de***file为依赖文件

command //具体编译命令

test.o : test.h test.c

gcc -c test.c -o test.o

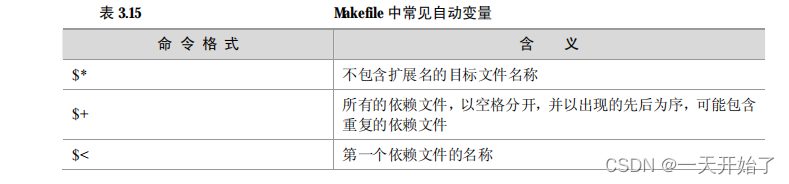

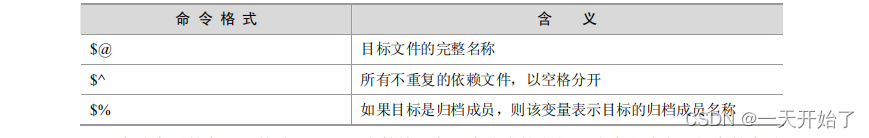

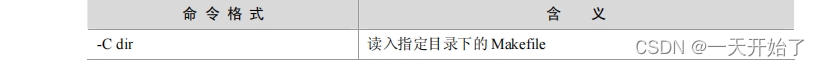

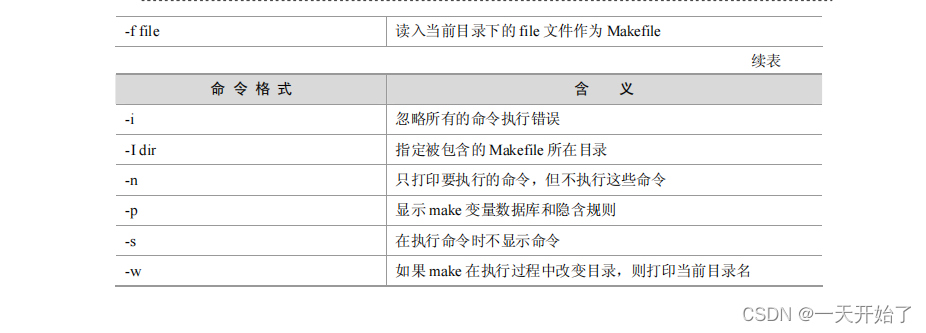

常用命令

例子

ARFLAGS = rcv

ARFLAGS_SO = $(LIBS_LD_CFLAGS)

ARFLAGS_SO += -shared -fPIC -o

CFLAGS += -Wall -fPIC -D$(HI_FPGA)

CFLAGS += -O2

TARGETLIB := test.a

TARGETLIB_SO := test.so

all:$(TARGETLIB)

$(TARGETLIB):$(OBJS)

@($(AR) $(ARFLAGS) $(TARGETLIB) $(OBJS))

@($(CC) $(ARFLAGS_SO) $(TARGETLIB_SO) $(OBJS))

@mkdir -p $(REL_LIB)

@cp $(TARGETLIB_SO) $(REL_LIB)

@cp $(TARGETLIB) $(REL_LIB)

# echo "print<<< $(REL_LIB) >>>" //该方法可以查看变量,对于新手有一定帮助

clean:

@$(RM) -rf $(TARGETLIB) $(OBJS)

@$(RM) -rf $(LIBPATH) $(OBJPATH)

aa:

echo "$(INC)"

文章来源:https://blog.csdn.net/qq_52575999/article/details/135003617

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!