DSP2335的时钟PLL配置

2024-01-08 23:43:46

PLL模块框图

xclkin是直接进来的外部时钟;

而下面的是振荡器(晶振出来)的时钟

PLLSTS 锁相环状态寄存器? ? ?PLLCR? 锁相环控制寄存器

PLLSTS【oscoff】 决定着外部时钟的输入

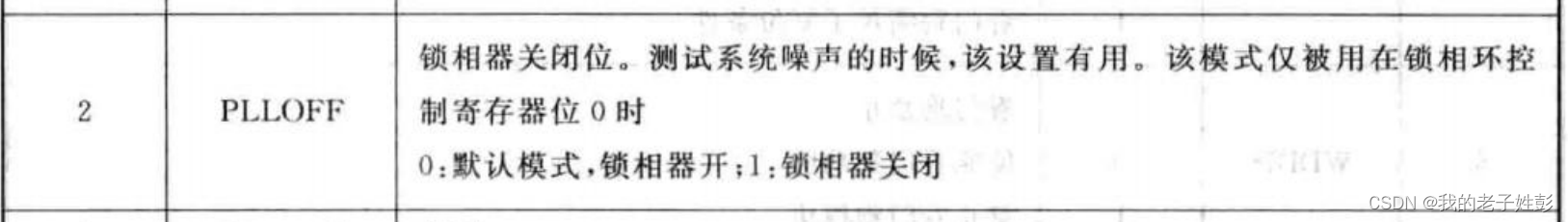

PLLSTS【plloff】? ?锁相器关闭位? 0使能PLL

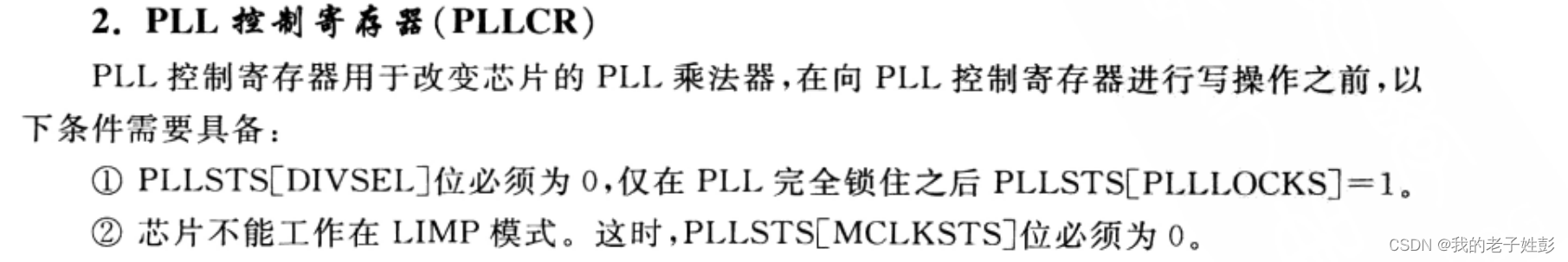

锁相环控制寄存器用于控制芯片 PLL 的倍数,在向 PLL 控制寄存器进行写操

作之前,需要具备以下两个条件。

(1)在 PLL 完全锁住后,即 PLLSTS[PLLLOCKS]=1。

(2)芯片不能工作在 LIMP 模式,即 PLLSTS[MCLKSTS]=0。

PLLSTS寄存器

mclksts判断此位不能是1,如果是1

使用mclkclr位写1,mclksts清零此位

PLLCR 寄存器

DIV就是旁路PLL,即pLL配置了,不通给不作为系统时钟;

使用此PLLCR寄存器额外注意需要PLLSTS? DIVSEL=0;

DIV设置好了,等待锁相环锁住就完成配置了

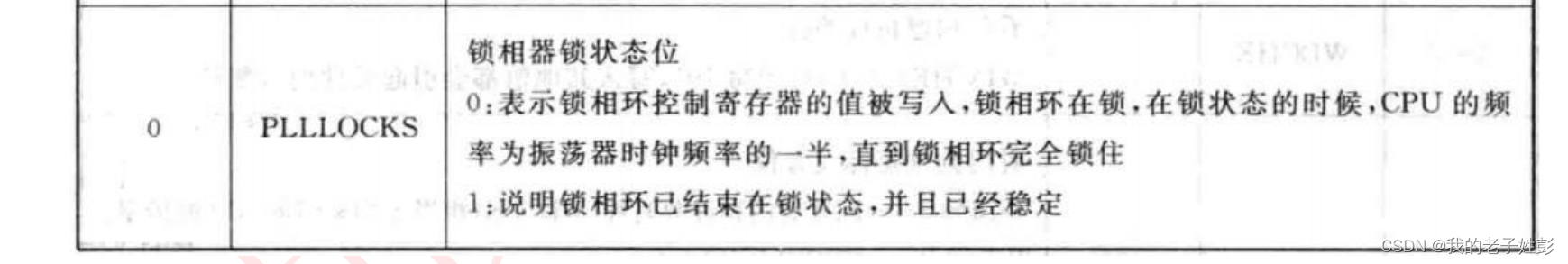

使用此寄存器倍频后,等待PLLSTS寄存器的PLLLOCK位=1完全锁住如下说明

最后通过PLLSTS【DIVSEL】分频送进系统时钟

最终的系统频率=输入时钟*DIV/DIVSEL? ?div 有对应的表? DIVSEL也是

程序

void InitPll(Uint16 val, Uint16 divsel)//12 2

{

volatile Uint16 iVol;

if (SysCtrlRegs.PLLSTS.bit.MCLKSTS != 0)//时钟信号丢失位 1为丢失

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.MCLKCLR = 1;//时钟信号丢失 清除/复位

EDIS;

asm(" ESTOP0"); // Uncomment for debugging purposes

}

if (SysCtrlRegs.PLLSTS.bit.DIVSEL != 0)//如果分频了

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 0;//设置为不分

EDIS;

}

if (SysCtrlRegs.PLLCR.bit.DIV != val)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1;//丢失时钟检测关闭位 关闭

SysCtrlRegs.PLLCR.bit.DIV = val;//倍频

EDIS;

DisableDog();

while(SysCtrlRegs.PLLSTS.bit.PLLLOCKS != 1)//等待锁相器锁上 等于1

{

}

EALLOW;

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 0;//丢失时钟检测关闭位 开启

EDIS;

}

if((divsel != 2)) //

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = divsel;//采用2分

EDIS;

}

}

文章来源:https://blog.csdn.net/qq_36658033/article/details/135467192

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!