vivado约束方法1

关于约束方法

设计约束定义了编译流必须满足的要求,以便设计要在板上发挥作用。中的所有步骤都不使用所有约束编译流程。例如,物理约束仅在实施过程中使用步骤(即通过放置器和路由器)。因为AMD Vivado?集成设计环境(IDE)的综合与实现算法是定时驱动的,您必须创建适当的定时约束。过度约束或设计约束不足会使时间闭合变得困难。你必须使用合理的与您的应用程序需求相对应的约束。

组织约束

Vivado IDE允许您使用一个或多个约束文件。使用单个约束文件时因为整个编译流程看起来更方便,所以维护所有程序可能是一个挑战随着设计变得越来越复杂,限制也越来越大。这种情况通常适用于使用由不同团队开发的几个IP核心或大块。导入时间和物理约束后,与数量无关源文件,或者无论设计是在项目模式还是非项目模式下,所有约束都可以使用write_xdc命令导出为单个文件。约束被写入指定的输出文件,其顺序与将它们读入项目或设计的顺序相同。这个命令行选项write_xdc-type可以用于选择约束的子集(定时,物理或弃权)。

项目流程

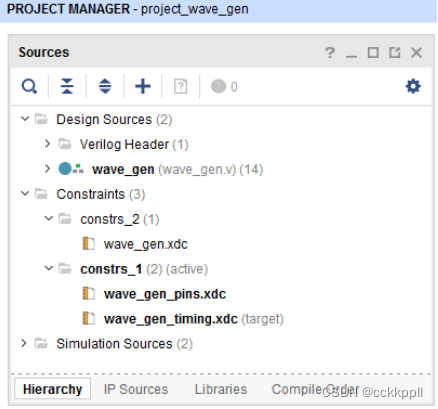

您可以在创建期间将Xilinx设计约束(XDC)文件添加到约束集新项目,或更高版本。下图显示了项目中的两个约束集,它们是单XDC或多XDC。这个第一个约束集包括两个XDC文件。第二个约束集仅使用一个XDC文件包含所有约束。

还可以将Tcl脚本添加到约束集中,作为非托管约束或非托管Tcl脚本。Vivado Design Suite不会将修改后的约束写回非托管Tcl剧本Tcl脚本和XDC文件的加载顺序与Vivado IDE中显示的顺序相同

(如果它们属于同一PROCESSING_ORDER组)或由命令报告report_compile_order-约束。

如果需要,可以在多个约束集中使用XDC文件或Tcl脚本。

非项目流程

在非项目模式下,在执行编译之前,必须单独读取每个文件命令。

下面的示例脚本显示了如何使用一个或多个XDC文件进行合成和实施

断章取义的约束

在使用动态函数eXchange(DFX)的设计中,通常会合成断章取义的设计(OOC)方法。当使用这样的流时,一些约束可以是仅为OOC合成指定。例如,在输入边界传播的时钟当块被OOC合成时,必须定义块的。这些时钟是定义的在OOC XDC文件中。

在项目模式下:

也可以通过GUI(文件上的属性constraints_oc.xdc)。

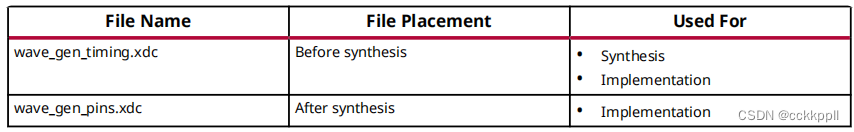

合成和实现约束文件

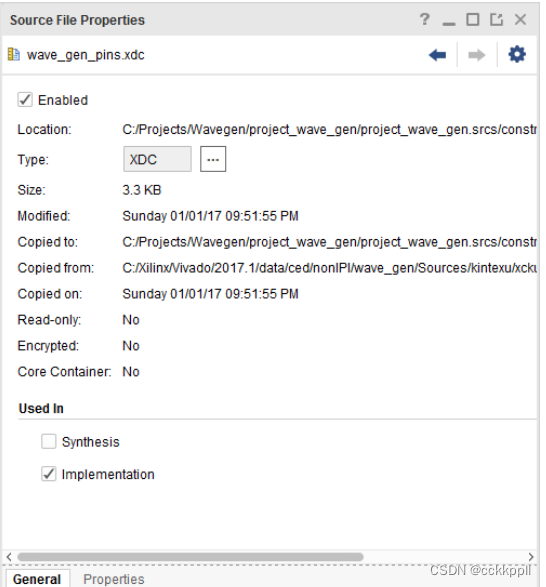

默认情况下,添加到约束集的所有XDC文件和Tcl脚本都用于合成和实施在上设置USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION属性XDC文件或Tcl脚本来改变这种行为。此属性的值可以为正确或错误。

例如,要仅将约束文件用于实现,请执行以下操作:

1.在“源”窗口中选择约束文件。

2.在“源文件属性”窗口中:

a.取消选中“合成”。

b.检查执行情况。

在非项目模式下运行Vivado时,可以直接读入任何流程的步骤。属性USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION做在这种模式下无关紧要。下面的编译Tcl脚本显示了如何为的不同步骤读取两个XDC文件流量:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!